Hindawi Scientific Programming Volume 2020, Article ID 4176794, 19 pages https://doi.org/10.1155/2020/4176794

# Review Article

# Survey of Methodologies, Approaches, and Challenges in Parallel Programming Using High-Performance Computing Systems

# Paweł Czarnul , 1 Jerzy Proficz, 2 and Krzysztof Drypczewski 2

- <sup>1</sup>Dept. of Computer Architecture, Faculty of Electronics, Telecommunications and Informatics, Gdansk University of Technology, Gdańsk, Poland

- <sup>2</sup>Centre of Informatics-Tricity Academic Supercomputer & Network (CI TASK), Gdansk University of Technology, Gdańsk, Poland

Correspondence should be addressed to Paweł Czarnul; pczarnul@eti.pg.edu.pl

Received 11 October 2019; Accepted 30 December 2019; Published 29 January 2020

Guest Editor: Pedro Valero-Lara

Copyright © 2020 Paweł Czarnul et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

This paper provides a review of contemporary methodologies and APIs for parallel programming, with representative technologies selected in terms of target system type (shared memory, distributed, and hybrid), communication patterns (one-sided and two-sided), and programming abstraction level. We analyze representatives in terms of many aspects including programming model, languages, supported platforms, license, optimization goals, ease of programming, debugging, deployment, portability, level of parallelism, constructs enabling parallelism and synchronization, features introduced in recent versions indicating trends, support for hybridity in parallel execution, and disadvantages. Such detailed analysis has led us to the identification of trends in high-performance computing and of the challenges to be addressed in the near future. It can help to shape future versions of programming standards, select technologies best matching programmers' needs, and avoid potential difficulties while using high-performance computing systems.

#### 1. Introduction

In today's high-performance computing (HPC) landscape, there are a variety of approaches to parallel computing that enable reaching the best out of available hardware systems. Multithreaded and multiprocess programming is necessary in order to make use of the growing computational power of such systems that is available mainly through the increase of the number of cores, cache memories, and interconnects such as Infiniband or NVLink [1]. However, existing approaches allow programming at various levels of abstraction that affects ease of programming, also through either onesided or two-sided communication and synchronization modes, targeting shared or distributed memory HPC systems. In this work, we discuss state-of-the-art methodologies and approaches that are representative of these aspects. It should be noted that we describe and distinguish the approaches by programming methods, supported languages, supported platforms, license, ease of programming,

deployment, debugging, goals, parallelism levels, and constructs including synchronization. Then, based on detailed analysis, we present current trends and challenges for development of future solutions in contemporary HPC systems.

Section 2 motivates this paper and characterizes the considered APIs in terms of the aforementioned aspects. Subsequent sections present detailed discussion of APIs that belong to particular groups, i.e., multithreaded processing in Section 3, message passing in Section 4, Partitioned Global Address Space in Section 5, agent-based parallel processing in Section 6 and MapReduce in Section 7. Section 8 provides detailed classification of approaches. Section 9 discusses trends in the development of the APIs including latest updates and changes that correspond to development directions as well as support for hybrid processing, very common in contemporary systems. Based on our extensive analysis, we formulate challenges in the field in Section 10. Section 11 presents existing comparisons, especially

performance oriented, of subsets of the considered APIs for selected practical applications. Finally, summary and planned future work are included in Section 12.

#### 2. Motivation

In this paper, we aim at identifying key processing paradigms and their representatives for high-performance computing and investigation of trends as well as challenges in this field for the near future. Specifically, we distinguish the approaches by the types of systems they target, i.e., shared memory, distributed memory, and hybrid ones. This aspect typically refers to workstation/server, clusters, and systems incorporating various types of compute devices, respectively.

Communication paradigms are request-response/twosided vs one-sided communication models. This aspect defines the type of a parallel programming API.

Abstraction level in terms of detailed level of communication and synchronization routines invoked by components is executed in parallel. This aspect is related to potential performance vs ease of programming of a given solution, i.e., high performance at the cost of more difficult programming for low level vs lower performance with easier programming using high-level constructs. Specifically, this approach distinguishes the following groups: low-level communication (just basic communication API), APIs with interthread, interprocess synchronization routines (MPI, OpenMP, etc.) that still requires much knowledge and awareness of the environment as well as framework-level programming. The authors realize that the presented assessment of ease of programming is subjective; nevertheless, it is clear that aspects like the number of lines of code to achieve parallelization are correlated with technology abstraction level.

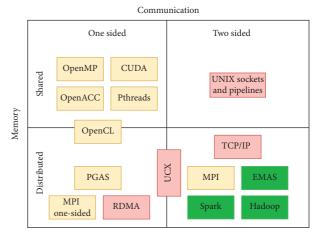

The considered approaches and technologies have been superimposed on a relevant diagram and shown in Figure 1. We realize that this is our subjective selection, with many other available technologies like C++11 thread.h library [2] or Threading Building Blocks [3] (TBBs), High Performance ParalleX [4] (HPX), and others. However, we believe that the above collection consists of representative technologies/APIs and can be used as a strong base for the further analysis. Moreover, selection of these solutions is justified by the existence of comparisons of subsets of these solutions presented in Section 11 and discussed in other studies.

Data visualization is an important part of any HPC system, and GPGPU technologies such as OpenGL and DirectX received a lot of attention in recent years [5]. Even though they can be used for general purpose computations [6], the authors do not perceive those approaches to become the main track of the HPC technology.

#### 3. Multithreaded Processing

In the current landscape of popular parallel programming APIs aimed at multicore and many-core CPUs, accelerators such as GPUs, and hybrid systems, there are several popular solutions [1] and descriptions of the most important ones in the following.

FIGURE 1: Abstraction level marked with colors: high, green; middle, yellow; low, red.

3.1. OpenMP. OpenMP [7] allows development and execution of multithreaded applications that can exploit multicore and many-core CPUs within a node. Latest OpenMP versions also allow offloading fragments of code to accelerators including GPUs. OpenMP allows relatively easy extension of sequential applications into a parallel application using two types of constructs: library functions that allow determination of the number of threads executing a region in parallel or thread ids and directives that instruct how to parallelize or synchronize execution of regions or lines of code. Mostly used directives include #pragma omp parallel spawning threads working in parallel in a given region as well as #pragma omp for allowing assignment of loop iterations to threads in a region for parallel processing. Various scheduling modes including static and dynamic with predefined chunk sizes with a guided mode with a decreasing chunk size are also available. It is also possible to find out the number of threads and unique thread ids in a region for fine-grained assignment of computations. OpenMP allows for synchronization through constructs such as critical sections, barrier, and atomic and reduction clauses. Latest versions of OpenMP support a task model in which a thread working in a parallel region can spawn tasks which are automatically assigned to available threads for parallel processing. A wait-directive imposing synchronization is also available [1].

3.2. CUDA. CUDA [8] allows development and execution of parallel applications running on 1 or more NVIDIA GPUs. Computations are launched as kernels that operate on and produce data. Synchronization of kernels and GPUs is performed through the host side. Parallel processing is executed by launching a grid of threads which are grouped into potentially many thread blocks. Threads within a block can be synchronized and can use faster albeit much smaller shared memory, compared to the global memory of a GPU. Shared memory can be used as a cache for intermediate storage of data as can be registers. When operating on data chunks, data can be fetched from global memory to registers

and from registers to shared memory to allow data prefetching. Similarly, RAM to GPU memory communication, computations within a kernel and GPU memory to RAM communication can be overlapped when operations are launched to separate CUDA streams. On the other hand, selection of the number of threads in a block can have an impact on performance as it affects the total block requirements for the number of registers and shared memory and considering limits on the numbers of registers and amount of shared memory per Streaming Multiprocessor (SM), it can affect the number of resident blocks and level of parallelization. Modern cards with high compute capability along with new CUDA toolkit versions allow for dynamic parallelism allowing launching a kernel from within a kernel as well as Unified Memory between the host and the GPU. CPU+GPU parallelization, similar to OpenCL, requires cooperation with another multithreading CPU API such as OpenMP or Pthreads. Multi-GPU systems can be handled with the API which allows to set a given active GPU which allows to do it from either one or many host threads to handle such systems. NVIDIA provides CUDA MPS for automatic overlapping and scheduling calls to even a single GPU from many host processes using e.g. MPI for interprocess communication.

3.3. OpenCL. OpenCL [9] allows development and execution of multithreaded applications that can exploit several compute devices within a computing platform such as a server with multiple multicore and many-core CPUs as well as GPUs. Computations are launched as kernels that operate on and produce data, within a so-called context defined for one or more compute devices. Work items within potentially many work groups execute the kernel in parallel. Memory objects are used to manage data within computations. OpenCL uses an analogous structure of an application to CUDA where work items correspond to threads and work groups to thread blocks. Similarly to CUDA, work items within a group can be synchronized. Since OpenCL extends the idea of running kernels on many and various (such as CPUs and GPUs) devices, it typically requires many more lines of device management code than a CUDA program. Similarly to CUDA streams, OpenCL uses the concept of command queues, into which commands such as data copy or kernel launches can be inserted. Many command queues can be used and execution can be synchronized by referring to events that are associated with commands. Additionally, the so-called local memory (similarly to what is called shared memory in CUDA) can be shared among work items within a single work group for fast access as cache-type memory. Shared virtual memory allows us to share complex data structures by the host and device sides.

3.4. Pthreads. Pthreads [1] allows development and execution of multithreaded applications on multicore and many-core CPUs. Pthreads allows a master thread to call a function that launches threads that execute code of a given function in parallel and then join the execution of the threads. The Pthreads API offers a wide array of functions, especially

related to synchronization. Specifically, mutexes are mutual exclusion variables that can control access to a critical section in the case of several threads. Furthermore, the so-called condition variables along with mutexes allow a thread to wait on a condition variable if a condition is not met. Another thread that has changed the condition can wake up a thread or several threads waiting for the condition. This scheme allows implementation of, e.g., the producer-consumer pattern without busy waiting. In this respect, Pthreads allows expression of more complex synchronization patterns than, e.g., OpenMP.

3.5. OpenACC. OpenACC [10] allows development and execution of multithreaded applications that can exploit GPUs. OpenACC can be seen as similar to OpenMP [11] in terms of abstraction level but focused on parallelization on GPUs through directives instructing parallelization of specified regions of code, scoping of data, and synchronization as well as library function calls. The basic #pragma acc parallel directive specifies execution of the following block by one or more gangs, each of which may run one or more workers. Another level of parallelism includes vector lanes within a worker. A region can be marked as one that can be executed by a sequence of kernels done with #pragma acc kernels while parallel execution of loop iterations can be specified with #pragma acc loop. Directives such as #pragma acc data can be used for data management with specification of allocation copy and freeing space on a device. Reference counters to data are used. An atomic #pragma acc directive can be used for accessing data.

3.6. Java and Scala. Java [12] and Scala [13] are Java Virtual Machine- (JVM-) [14] based languages; both are translated into JVM byte codes and interpreted or further compiled into a specific hardware instruction set. Thus, it is natural that they share common mechanisms for supporting the concurrent program execution. They provide two abstraction levels of the concurrency, the lower one which is related directly to operating system/hardware-based threads of control and the higher one, where the parallelism is hidden by the executor classes, which are used to schedule and run user-defined tasks.

A Java thread can be used when direct control of the concurrency is necessary. Its life cycle is strictly controlled by the programmer; he or she can create and provide its content: the list instructions to be executed concurrently, monitor, interrupt, and finish. Additionally, API is provided that supports thread interactions, including synchronization and in-memory data exchange.

The higher level concurrency objects support parallel code execution in more complex applications, where the fine level of thread control is not necessary, but parallelization can be easily provided for larger groups of compute tasks. Concurrent collections can be used for parallel access to inmemory data, lock classes enable nonblocking access to synchronized code, atomic variables help to minimize synchronization and avoid consistency issues, and the executor classes manage thread pools for queuing and scheduling of compute tasks.

# 4. Message Passing Processing

4.1. Low-Level Communication Mechanisms. The low-level communication mechanisms are used by HPC frameworks and libraries to enable data transmission and synchronization control. From the network point of view, the typical approach is to provide a network stack, with the layers corresponding to different levels of abstraction. TCP/IP is a classical stack provided in the most modern systems, not only in HPC. Usually, its main goal is to provide means to exchange data with external systems, i.e., Internet access; however, it can be also used to support computations directly as a medium of data exchange.

Nowadays, TCP/IP [15] can be perceived as a reference network stack, although the ISO-OSI is still reminded to be used for this purpose [16]. Figure 2(a) presents the TCP/IP layer structure: link—the lowest one is responsible for handling hardware, IP—the second one provides simple routed transmission of the packages, transport—the third one is usually used by the communication frameworks or directly by the applications for either connection-based protocol: Transmission Control Protocol (TCP) or for connection-less datagram transmission: User Datagram Protocol (UDP).

The other, quite often application/framework API used in HPC, is Remote Direct Memory Access (RDMA) [17]. Similarly to the TCP/IP, its stack has layered structure and its lowest layer link is responsible for handling the hardware. Currently, two main hardware solutions are used: Infiniband, the intraconnecting network characterized by multicast support, high bandwidth, low latency, and an extended version of Ethernet, with RDMA over Converged Ethernet v1 (RoCEv1) protocol [18], where multicast transmission is supported in a local network (see Figure 2(b)). The test results presented in [19] showed performance advantages of a pure Infiniband solution; however, introduction of RoCE enabled great latency reduction in comparison with classical Ethernet.

Figure 2(c) presents RDMA over Converged Ethernet v2 (RoCEv2) [20], where RDMA is deployed over plain IP stack, on top of the UDP protocol. In this case, some additional requirements over the protocol implementation are introduced: ordering of the transmitted messages and some congestion control mechanism. Usage of UDP packets, which are routable, implies that the communication is not limited to one local network, and that is why RoCEv2 is sometimes called Routable RoCE (RRoCE).

The Unified Communication X (UCX) [21] is a network stack providing a collection of APIs dedicated to support different middleware frameworks: Message Passing Interface (MPI) implementations, Partitioned Global Address Space (PGAS) languages, task-based paradigms, and I/O bound applications. This initiative is a combined effort of the US national laboratories, industry, and academia. Figure 2(d) presents its architecture with link layer split into hardware and driver parts, where the former is responsible for physical connection and the latter provides vendor-specific functionality used by the higher layer, which is represented by two APIs: UC-T supporting low level hardware-transport functionality and UC-S with common utilities. Finally, the highest layer provides UC-P collections of protocols, where

specific platforms or even applications can find the proper communication and/or synchronization mechanisms.

The UCX reference implementation presented promising results in performed benchmarks, showing the measurements being very close to the underlying driver capabilities, as well as providing the highest publicly known bandwidth for a given hardware. The above results were confirmed by benchmarks executed on OpenSHMEM [22] PGAS platform, where, on the Cray XK, in most test cases, UCX implementation outperformed the one provided by the vendor [23]. In [24], comparison of performance of UC-P and UC-T on InfiniBand is presented. Even though UC-T was more efficient, optimizations proposed by Papadopoulou et al. suggest that there is a room to improve performance of higher level UC-P.

Finally, for the sake of completeness, we need to mention UNIX sockets and pipeline mechanisms [25], which are quite similar to TCP/IP ones; however, they work locally within a boundary of a single server/workstation, managed by the UNIX-based operating system. Usually, the sockets support stream and datagram messaging, similar to the TCP/IP approach, but since they work on the local machine, the data transfer is reliable and properly sequenced. The pipelines provide a convenient method for data tunneling between the local processes and usually correspond to the standard output and input streams.

4.2. MPI. The Message Passing Interface (MPI) [26] standard was created for enabling development and running parallel applications spanning several nodes of a cluster, a local network, or even distributed nodes in grid-aware MPI versions. MPI allows communication among processes or threads of an MPI application primarily by exchanging messages—message passing. MPI is a standard, and there are several popular implementations of the standard, examples of which are MPICH [27] and OpenMPI [28].

Key components of the standard, in the latest 3.1 version, define and include the following:

- (1) Communication routines: point-to-point as well as collective (group) calls

- (2) Process groups and topologies

- (3) Data types including calls for definition of custom data types

- (4) Communication contexts, intracommunicators, and intercommunicators for communication within a group or among groups of processes

- (5) Creation of processes and management

- (6) One-sided communication using memory windows

- (7) Parallel I/O for parallel reading and writing from/to files by processes of a parallel application

- (8) Bindings for C and Fortran

## 5. Partitioned Global Address Space

Partitioned Global Address Space (PGAS) is an approach to perform parallel computations using a system with

| Application/<br>framework | Application/<br>framework | Application/<br>framework | Application/<br>framework |  |

|---------------------------|---------------------------|---------------------------|---------------------------|--|

| TCP/UDP<br>transport      | IB transport              | IB transport              | UC-P                      |  |

| IP                        | IB                        | UDP                       | UC-T/UC-S                 |  |

| II.                       | 115                       | IP                        | 00-1/00-3                 |  |

| Link                      | Link                      | Link                      | Drivers                   |  |

| LIIIK                     | LillK                     | Link                      | Hardware                  |  |

| (a)                       | (b)                       | (c)                       | (d)                       |  |

FIGURE 2: Main network stacks used in HPC: (a) TCP/IP, (b) RDMA over Infiniband/RoCEv1, (c) RDMA over RoCEv2, and (d) UCX.

potentially distributed memory. The access to the shared variables is possible by a special API, supported by a middleware implementing data transmission, synchronization, and possible optimization, e.g., data prefetch. Such a way of communication, when the data used by many processes are updated only by one, without activities taken by the other is called one-sided communication.

The classical example of PGAS realization is Open-SHMEM [22] specification, which provides a C/Fortran API for data exchange and process synchronization with distributed shared memory. Each process, potentially assigned to a different node, can read and modify a common pool of the variables as well as use a set of synchronization functions, e.g., invoking barrier before data access. This initiative is supported by a number of organizations including CRAY, HPE, Intel, Mellanox, US Department of Defense, and Stony Brook University. The latter one is responsible for an OpenSHMEM reference implementation.

Another notable PGAS implementation is Parallel Computing in Java [29] (PCJ), providing a library of functions and dedicated annotations for distributed memory access over an HPC cluster. The proposed solution uses Java language constructs like classes, interfaces, and annotations for storing and exchanging common data between the cooperating processes, potentially placed in different Java Virtual Machines on separated cluster nodes. There are other typical PGAS mechanisms like barrier synchronization or binomial tree-based vector reduction. The executed tests showed good performance of the proposed solution in comparison with an MPI counterpart.

In our opinion, the above selection consists of representative examples of PGAS frameworks; however, there are many more implementations of this paradigm, e.g., Chapel [30] and X10 [31] parallel programming languages, Unified Parallel C [32] (UPC), or C++ Standard Template Adaptive Parallel Library [33] (STAPL).

#### 6. Agent-Based Parallel Processing

Soft computing is a computing paradigm that allows solving problems with an approach similar to the way a human mind reasons and provides good enough approximations instead of precise answers. Soft computing includes many computing techniques including machine learning, fuzzy logic,

Bayesian networks, and genetic and evolutionary algorithms. A multiagent system (MAS) is a soft computing system that consists of an environment and a set of agents. Agents communicate, negotiate, and cooperate with each other and act in way that can change their own state or the state of the environment. MAS aims to provide solutions acquired from knowledge base acquired from evolutionary process. Kisiel-Dorohinicki et al. [34] distinguished the following complexity-based MAS types: (1) traditional model based of fuzzy logic in which evolution occurs on the agent level, (2) evolutionary multiagent systems (EMAS) in which evolution occurs on population level of homogeneous agents, and (3) MAS with heterogeneous agents that use different types of soft computing methods. Kisiel-Dorohinicki [35] proposed a decentralized EMAS model based on an M-Agent architecture. Agents have profiles that inform about actions taken. Profiles consist of knowledge about environment, acquired resources, goals, and strategies to be achieved. In EMAS, similarly to organic evolution, agents can reproduce (create new, sometimes changed agents) and die according to agent fitness and changes in the environment. Selection for reproduction and death is a nontrivial problem, since agents have their autonomy and there is no global knowledge. Agents obtain nonrenewable resource called life energy that is obtained as a reward or lost as a penalty. Energy level specifies actions that agents can perform.

Several general purpose agent modeling frameworks were proposed. Repast [36] is an open-source toolkit for agent simulation. It provides functionality for data analysis with special focus on agent storage, display, and behavior. Repast scheduler is responsible for running user-defined "actions," i.e., agent actions. The scheduler orders actions in tree structures that describe execution flow. This allows for dynamic scheduling during model tick, i.e., an action performed by an agent generates a new action in response [37]. Repast HPC aims to provide Repast functionality in an HPC environment. It uses a scheduler that sorts agent actions (timeline and relation between agent relations) and MPI to parallelize computations. Each process typically handles one or more agents and is responsible for executing local actions. Then, the scheduler aggregates information for the current tick and enables communication between related agents [38]. EUR-ACE is an agent-based system project that tries to model European Economy [39]. Agents communicate between each

other by sending messages. To reduce the amount of data exchanged between agents, it groups them into local groups. It leverages the idea that agents will typically communicate with a small number of other agents that should be processed as closely as possible (i.e., different processes on the same machine instead of different cluster nodes).

### 7. MapReduce Processing

7.1. Apache Hadoop. Apache Hadoop is a programming tool and framework allowing distributed data processing. It is an open source implementation of Google's MapReduce [40]. The Hadoop MapReduce programming model is dedicated for processing large amounts of data. Computation is split into small tasks that are executed in parallel in the machines of the cluster. Each task is responsible for processing only small part of data and thus reducing resource requirements. This approach is very scalable and can be used both on high end and commodity hardware. Hadoop handles all typical problems connected with data processing like fault tolerance (repeating computation that failed), data locality, scheduling, and resource management.

First Hadoop versions were designed and tailored for handling web crawler processing pipelines which provided some challenges for adoption of MapReduce for wider types of problems. Vavilapalli et al. [41] describe design and capabilities of Yet Another Resource Negotiator (YARN) that aims to disjoin resource management and programming model and provide extended scheduling settings. YARN moves from original architecture to match modern challenges such as better scalability, multiuser support ("multitenancy"), serviceability (ability to perform a "rolling upgrade"), locality awareness (moving computation to data), reliability, and security. YARN [42] also includes several types of basic mechanisms for handling resource requests: FAIR, FIFO, and capacity schedulers.

Apache Hadoop was deployed by Yahoo in early 2010s and achieved high utilization on a large cluster. Nevertheless, energy efficiency was not satisfactory, especially when heavy loads were not present. Leverich and Kozyrakis [43] pointed out that (due to its replication mechanism) Hadoop Distributed Files System (HDFS) precluded scaling down clusters. The authors proposed a solution in which a cluster subset must contain blocks of all required data, thus allowing processing only on this subset of nodes. Then, additional nodes can be added if needed and removed when load is reduced. This approach allowed for reducing power consumption even up to 50% but the achieved energy efficiency was accompanied with diminished performance.

Advancements in high-resolution imaging and decrease in cost of computing power and IoT sensors lead to substantial growth in the amount of generated spatial data. Aji et al. [44] presented Hadoop-based geographical information system (GIS) for warehousing large-scale spatial datasets that focuses on expressive and scalable querying. The proposed framework parallelizes spatial queries and maps them to MapReduce jobs. Hadoop GIS includes mechanism for boundary handling especially in context of data partitioning.

In recent years, several algorithms extending capabilities of Hadoop MapReduce were proposed [45]. Hadoop schedulers do not allow setting time constraints for job execution. Kc and Anyanwu [46] present a scheduling algorithm for meeting deadlines that ensures that only jobs that can finish in user-defined time frame are scheduled. The algorithm takes into consideration the number of available map and reduces task slots for a job that has to process the set amount of data and estimates if the deadline can be kept on the cluster of a predefined size. Ghodsi et al. [47] proposed the Domain Resource Fairness (DRF) allocation algorithm for providing fair share in a system with heterogeneous resources (e.g., two jobs may require similar memory, but different amount of CPU time). DRF aims to provide dominant share, i.e., demands weight which mostly depends on max-min fairness of dominant resource. Longest Approximate Time to End (LATE) [48] scheduling policy aims to offer better performance for heterogeneous clusters. LATE does not assume that that tasks progress linearly or that each machine in cluster has the same performance (which is important in virtualized environments). In case of tasks that perform slower than expected ("stragglers"), Hadoop runs duplicate ("speculative") task on different nodes to speed up processing. LATE improves the heuristics that recognize stragglers by taking into consideration not only the current progress of the task but also the progress rate.

7.2. Apache Spark. Hadoop MapReduce became a very popular platform for distributed data processing of large datasets. Even though its programming model is not suitable for several types of applications. An example of those would be interactive operations on data sets such as data mining or fast custom querying and iterative algorithms. In the first case, intermediate processing results could be saved in memory instead of being recomputed, thus improving performance. In the second case of input data, iterative map tasks read input data for each iteration, thus requiring repetitive, costly disk operations.

Apache Spark is a cluster computing framework designed to solve the aforementioned issues and allow MapReduce style operations on streams. It was proposed in 2010 [49] by AMPLab and later became Apache Foundation project. Similarly to MapReduce, the Spark programming model allows the user to provide directed acyclic graph of tasks which are executed on the machines of the cluster.

The most important part of Spark is the concept of a Resilient Distributed Dataset (RDD) [50], which represents an abstraction for a data collection that is distributed among cluster nodes. RDD provides strong typing and ability to use lazily evaluated lambda functions on the elements of the

The Apache Spark model is versatile enough to allow us to run diverse types of applications and many big data processing platforms run heterogeneous computing hardware. Despite that, most big data oriented schedulers expect to run in an homogeneous environment both in context of applications and hardware. Heterogeneity-Aware Task

Scheduler RUPAM [51] takes into consideration not only standard parameters like CPU, RAM, and data locality but also include parameters like disk type (HDD/SDD), availability of GPU or accelerator, and access to remote storage devices. RUPAM reduced execution time up to 3.4 times in the tested cluster.

Spark allows multiple tasks to be run on a machine in the cluster. To improve performance, the colocation strategy must take into account characteristics of task's resource requirements. For example, if a task receives more RAM that it requires, the cluster throughput is reduced. If a task does not receive enough memory, it will not be able to finish, thus also affecting total performance. Due to this, developers often overestimate their requirements from schedulers. The strategy used by typical colocation managers to overcome these problems requires detailed resource usage data for each task type provided in situ or gathered from statistical or analytical models. Marco et al. [52] suggest a different approach using memory aware task colocation. Using machine learning, the authors created an extensive model for different types of tasks. The model is used during task execution to estimate its behavior and future resource requirements. The proposed solution increases average system throughput over 8x.

Similarly to Hadoop MapReduce, Spark recognizes tasks for which execution times are longer that expected. To improve performance, Spark uses speculative task execution to launch duplicates of slower tasks so that job can finish in a timely manner. This algorithm does not recognize sluggers, i.e., machines that run slower than other nodes in the cluster. To solve this problem, Data-Based Multiple Phases Time Estimation [53] was proposed. It provides Spark with information about estimated time of tasks which allows speculative execution to avoid slower nodes and increase of execution time up to 10.5%.

# 8. Classification of Approaches

In order to structure the knowledge about the approaches and exemplary APIs representing the approaches, we provide classifications in three groups, by

- (1) Abstraction level, programming model, language, supported platforms and license in Table 1—we can see that approaches at a lower level of abstraction support mainly C and Fortran, sometimes C++ while at a higher level distributed ones, Java/Scala

- (2) Goals (performance, energy, etc.), ease of programming, debugging, and deployment as well as portability in Table 2—we can see that ease of programming, debugging, and deployment increase with the level of abstraction

- (3) Level of parallelism, constructs expressing parallelism, and synchronization in Table 3—the latter ones are easily identified and are supported for all the presented approaches

We note that classification of the approaches and APIs in terms of target system types, distributed and shared memory systems, is shown in Figure 1. The APIs targeting

accelerators are intentionally regarded as shared memory referring to the device memory.

# 9. Trends in Scientific Parallel Programming

There are several sources that observe changes in the HPC arena and discuss potential problems to be solved in the near future. In this section, we collect these observations and then, along with observations, build towards formulation of challenges for the future in the next section.

Jack Dongarra underlines the progress in HPC hardware that is expected to reach the EFlop/s barrier in 2020-2021 [56]. It can be observed that most of the computational power in today's systems is grouped in accelerators. At the same time, old benchmarks do not fully represent current loads. Furthermore, benchmarks such as HPCG obtain only a small fraction of peak performance of powerful HPC systems today.

HPC can now be accessed relatively easily in a cloud and GPUs and specialized processors like tensor processing units (TPU) addressing artificial intelligence (AI) applications have become the focus with edge computing, i.e., the need for processing near mobile users being important for the future [57].

Energy-aware HPC is one of the current trends that can be observed in both hardware development as well as software solutions, both at the scheduling and application levels [58]. When investigating performance vs energy consumption tradeoffs, it is possible to find nonobvious (i.e., nondefault) configurations using power capping (i.e., other than the default power limit) for both multicore CPUs [59] as well as GPUs [60]. However, optimal configurations can be very different, depending on both the CPU/GPU types as well as application profiles.

A high potential impact of nonvolatile RAM (NVRAM) on high-performance computing has been confirmed in several works. The evaluation in [61] shows its potential support for highly concurrent data-intensive applications that exhibit big memory footprints. Work [62] shows a potential for up to 27% savings in energy consumption. It has also been shown that parallel applications can benefit from NVRAM used as an underlying layer of MPI I/O and serving as a distributed cache memory, specifically for applications such as multiagent large-scale crowd simulations [63], parallel image processing [64], computing powers of matrices [65], or checkpointing [66].

Trends in high-performance computing in terms of software can also be observed by following recent changes to the considered APIs. Table 4 summarizes these changes for the key APIs along with version numbers and references to the literature where these updates are described.

In the network technologies, we can see strong competition in performance factors, where especially the bandwidth is always a hot topic. New hardware and standards for Ethernet speeds beats subsequent barriers: 100, 400, ... GBps as well as the InfiniBand with its 100, 200, ... GBps. Thus, this rapid development gives the programmers opportunities to introduce more and more parallel solutions, which are well scalable even for large sizes of the problems. On the other hand, such race does not have a great impact on

TABLE 1: Target/model classification of technologies.

| Technology/<br>API  | Abstraction level/group | Programming model                                                                                                                                                                                      | Programming language                 | Supported platforms/target parallel system                                                                                                                | License/standard                                                                                    |

|---------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| OpenMP              | Library                 | Multithreaded application                                                                                                                                                                              | C/C++/Fortran                        | Heterogeneous system with CPU(s), accelerators including GPU(s) [54], supported by, e.g., gcc                                                             | OpenMP is a standard [7]                                                                            |

| CUDA                | Library                 | CUDA model,<br>computations launched as<br>kernels executed by<br>multiple threads grouped<br>into blocks, global, and<br>shared memory on the<br>GPU as well as host<br>memory for data<br>management | С                                    | Server or workstation with<br>1 + NVIDIA GPU(s)                                                                                                           | Proprietary NVIDIA<br>solution, NVIDIA<br>EULA [8] <sup>1</sup>                                     |

| OpenCL              | Library                 | OpenCL model,<br>computations launched as<br>kernels executed by<br>multiple work items<br>grouped into work groups<br>and memory objects for<br>data management                                       | C/C++                                | Heterogeneous platform<br>including CPUs, GPUs from<br>various vendors, FPGAs, etc.,<br>supported by, e.g., gcc                                           | OpenCL is a standard<br>[9]                                                                         |

| Pthreads            | Library                 | Multithreaded application, provides thread management routines, synchronization mechanisms including mutexes, conditional variables                                                                    | С                                    | Widely available in UNIX platforms, implementations, e.g., NPTL                                                                                           | Part of the POSIX<br>standard                                                                       |

| Open ACC            | Library                 | Multithreaded application                                                                                                                                                                              | C/C++/Fortran                        | Heterogeneous architectures,<br>e.g., a server or workstation<br>with x86/POWER + NVIDIA<br>GPUs, support for compilers<br>such as PGI, gcc, accULL, etc. | OpenACC is a standard [10]                                                                          |

| Java<br>Concurrency | JVM [14]<br>specific    | Multithreaded application                                                                                                                                                                              | Java, scala                          | Server, workstation, mobile device                                                                                                                        | Open standards: [12, 13]                                                                            |

| TCP/IP              | Network<br>stack        | Multi-process                                                                                                                                                                                          | C, Fortran, C++,<br>Java, and others | Cluster, server, workstation, mobile device, and others                                                                                                   | TCP/IP [15] is a<br>standard broadly<br>implemented by OS<br>developers                             |

| RDMA                | Network<br>stack        | Multiprocess                                                                                                                                                                                           | С                                    | Cluster                                                                                                                                                   | RDMA [17] is a<br>standard implemented<br>by over InfiniBand and<br>converged Ethernet<br>protocols |

| UCX                 | Network<br>stack        | Multiprocess,<br>multithreaded                                                                                                                                                                         | C, Java, Python                      | Cluster, server, workstation                                                                                                                              | UCX [21] is a set of<br>network APIs with a<br>reference<br>implementation                          |

| MPI                 | Library                 | Multiprocess, also<br>multithreaded if<br>implementation supports                                                                                                                                      | C/Fortran                            | Cluster, server, workstation                                                                                                                              | MPI is a standard [26],<br>several implementations<br>available, e.g., OpenMPI<br>and MPICH         |

| OpenSHMEM           | Library                 | Multiprocess application                                                                                                                                                                               | C, Fortran                           | Cluster                                                                                                                                                   | Open standard with reference implementation                                                         |

| PCJ                 | Java library            | Multiprocess application                                                                                                                                                                               | Java                                 | Cluster                                                                                                                                                   | Open source Java library [29]                                                                       |

Table 1: Continued.

| Technology/<br>API | Abstraction level/group | Programming model                                                                                                                             | Programming language                                       | Supported platforms/target parallel system | License/standard                                                                                   |

|--------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------|

| Apache<br>Hadoop   | Set of applications     | YARN managed resource<br>negotiation, multiprocess<br>MapReduce tasks [41]                                                                    | Core functionality<br>in JAVA, also C,<br>BASH, and others | Cluster, server, workstation               | Open source<br>implementation of<br>Google's MapReduce<br>[40], Apache software<br>license-ASL 2.0 |

| Apache Spark       | Set of applications     | Resource negotiation based<br>on the selected resource<br>manager (YARN, Spark<br>Standalone, etc.), executors<br>run workers in threads [49] | Scala                                                      | Cluster, server, workstation               | Apache software<br>license-ASL 2.0 [55]                                                            |

¹https://docs.nvidia.com/cuda/eula/index.html

TABLE 2: Technologies and goals.

|                    |                                   | TABLE 2. IC                                                                                                                                                                                                                                                                     | echnologies and goals.                                                                                                                |                                                                                                |                                                                                                                                                          |

|--------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Technology/<br>API | Goals (performance, energy, etc.) | Ease of programming                                                                                                                                                                                                                                                             | Ease of assessment, e.g., performance                                                                                                 | Ease of deployment/<br>(auto) tuning                                                           | Portability (between<br>hardware, for new<br>hardware, etc.)                                                                                             |

| OpenMP             | Performance,<br>parallelization   | Relatively easy, parallelization of a sequential program by addition of directives for parallelization of regions and optionally library calls for thread management, difficulty of implementing certain schemes, e.g., similar to those with Pthread's condition variables [1] | Execution times can<br>be benchmarked<br>easily, debugging<br>relatively easy                                                         | Easy, thread number can be set using an environment variable, at the level of region or clause | Available for all major<br>shared memory<br>environments, e.g., in<br>gcc                                                                                |

| CUDA               | Performance                       | Proprietary API, easy-to-<br>use in a basic version for a<br>default card, more difficult<br>for optimized codes<br>(requires stream handling,<br>memory optimizations<br>including shared<br>memory-avoiding bank<br>conflicts, global memory<br>coalescing)                   | Can be performed<br>using cuda-gdb or<br>very powerful nvvp<br>(NVIDIA visual<br>Profiler) or text-based<br>nvprof                    | Easy, requires CUDA<br>drivers and software                                                    | Limited to NVIDIA<br>cards, support for<br>various features depends<br>on hardware version-<br>card's CUDA compute<br>capability and software<br>version |

| OpenCL             | Performance                       | More difficult than CUDA<br>or OpenMP since it<br>requires much device and<br>kernel management code,<br>optimized code may<br>require specialized kernels<br>which somehow defies the<br>idea of portability                                                                   | Can be benchmarked<br>at the level of kernels,<br>queue management<br>functions can be used<br>for fencing<br>benchmarked<br>sections | Easy, requires proper<br>drivers in the system                                                 | Portable across hybrid<br>parallel systems,<br>especially CPU+GPU                                                                                        |

| Pthreads           | Performance                       | More difficult than OpenMP, flexibility to implement several multithreaded schemes, involving wait-notify, using condition variables for, e.g., producer- consumer                                                                                                              | Easy, thread's code in<br>designated functions,<br>and can be<br>benchmarked there                                                    | Easy, thread's code<br>executed in<br>designated functions                                     | Available for all major<br>shared memory<br>environments                                                                                                 |

Table 2: Continued.

|                     |                                   | 11121                                                                                                                                                                                        | E 2: Continued.                                                                                                                                                |                                                                                                                                                                                                                 |                                                                                                             |

|---------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Technology/<br>API  | Goals (performance, energy, etc.) | Ease of programming                                                                                                                                                                          | Ease of assessment,<br>e.g., performance                                                                                                                       | Ease of deployment/<br>(auto) tuning                                                                                                                                                                            | Portability (between<br>hardware, for new<br>hardware, etc.)                                                |

| OpenACC             | Performance                       | Easy, similar to the OpenMP's directive-based model, however requires awareness of overheads and corresponding needs for optimization related to, e.g., data placement, copy overheads, etc. | Standard libraries can<br>be used for<br>performance<br>assessment, gprof can<br>be used                                                                       | Requires a compiler<br>supporting<br>OpenACC, e.g., PGI's<br>compiler, GCC, or<br>accULL                                                                                                                        | Portable across compute<br>devices supported by the<br>software                                             |

| Java<br>Concurrency | Parallelization                   | Easy, two levels of abstraction                                                                                                                                                              | Easy debugging and profiling                                                                                                                                   | Easy deployment for many OS                                                                                                                                                                                     | Portable over majority of hardware                                                                          |

| TCP/IP              | Standard network connectivity     | Programming can be<br>difficult, requires<br>knowledge of low-level<br>network mechanisms                                                                                                    | Debugging can be<br>difficult, available<br>tools for time<br>measurement                                                                                      | Usually already deployed with the OS                                                                                                                                                                            | Portable over majority of hardware                                                                          |

| RDMA                | Performance                       | Programming can be<br>difficult, requires<br>knowledge of low-level<br>network mechanisms                                                                                                    | Debugging can be<br>difficult, available<br>tools for time<br>measurement                                                                                      | Deployment can be difficult                                                                                                                                                                                     | Usually used with clusters                                                                                  |

| UCX                 | Performance                       | Programming can be<br>difficult, it is library for<br>frameworks                                                                                                                             | Debugging can be<br>difficult, it is quite a<br>new solution                                                                                                   | Deployment can be difficult                                                                                                                                                                                     | Usually used with clusters                                                                                  |

| МРІ                 | Performance,<br>parallelization   | Relatively easy, high-level,<br>message passing paradigm                                                                                                                                     | Measurement of<br>execution time easy,<br>difficult debugging,<br>especially in a cluster<br>environment                                                       | Deployment can<br>require additional<br>tools, e.g., drivers for<br>advanced<br>interconnects such as<br>Infiniband or SLURM<br>for an HPC queue<br>system, tuning<br>typically based on<br>low-level profiling | Portable, implementations available on clusters, servers, workstations, typically used in Unix environments |

| OpenSHMEM           | Performance,<br>parallelization   | Easy, needs attention for synchronized data access                                                                                                                                           | No dedicated<br>debugging and<br>profiling tools                                                                                                               | Fairly easy<br>deployment in many<br>environments                                                                                                                                                               | Portable, implementations available on clusters, servers, workstations, typically used in UNIX environments |

| PCJ                 | Performance, parallelization      | Easy, classes and annotations used for object distribution                                                                                                                                   | No dedicated<br>debugging and<br>profiling tools                                                                                                               | Easy deployment for many OS                                                                                                                                                                                     | Portable over majority of hardware                                                                          |

| Apache<br>Hadoop    | Performance,<br>large datasets    | Relatively easy, high level<br>abstraction, requires good<br>understanding of<br>MapReduce programming<br>model                                                                              | Easy to acquire job performance                                                                                                                                | Moderately easy basic<br>deployment,<br>tweaking<br>performance, and<br>security for entire<br>hadoop ecosystem<br>can be very difficult                                                                        | Used in clusters,<br>available for Unix and<br>windows                                                      |

| Apache Spark        | disk, and high                    | Relatively easy, high-level<br>abstraction, based on<br>lambda functions on RDD<br>and dataFrames                                                                                            | Easy to acquire job<br>performance<br>overview (web UI and<br>logs), moderately easy<br>debugging, central<br>logging can be used to<br>streamline the process | Easy Spark<br>Standalone<br>deployment, Spark on<br>YARN deployment<br>requires a functioning<br>Hadoop ecosystem                                                                                               | Used in clusters,<br>available for Unix and<br>Windows                                                      |

the APIs, protocols, and features provided to the programmers, so the legacy software based on the lowest layer services does not need to be updated often.

We can observe that the frameworks and libraries are continuously extended and updated. We can see that some converging tendencies have already been present for a long

time, e.g., an introduction of offload for accelerator support in OpenMP or multithreading support in OpenSHMEM or MPI. The message to the users is that their favorite API will finally support new features of the most popular hardware or at least will give easy way to use it in collaboration with other technologies (e.g., the case of complementing MPI and OpenMP).

Hybrid parallelism has also become mainstream in high-performance computing due to hardware developments and heterogeneity in terms of various compute devices within a node or a cluster (e.g., CPUs+GPUs). This forces programmers to use combinations of APIs for efficient parallel programming, e.g., MPI+CUDA, MPI+OpenCL, or MPI+OpenMP+CUDA [1]. Table 5 summarizes hybridity present in various considered technologies including potential shortcomings as well as disadvantages.

# 10. Challenges in Modern High-Performance Computing

Similar to discussing trends, we mention selected works discussing expected problems and issues in the HPC arena for the nearest future. We then identify more points for an even more complete picture, in terms of the aspects discussed in Section 2.

Dongarra mentions several problematic issues [56] such as minimization of synchronization and communication of algorithms, using mixed precision arithmetics for better performance (low precision is already used in deep learning [72], for instance), designing algorithms to survive failures, and autotuning of software to a given environment.

According to [73], one of the upcoming challenges in Exascale HPC era will be energy efficiency. Additionally, software issues in HPC are denoted as open issues in this context, e.g., memory overheads and scalability in MPI, thread creation overhead in OpenMP, and copy overheads. Fault tolerance and I/O overheads for large-scale processing are listed as difficulties.

Both the need for autotuning and progress in software for modern HPC systems have also been stated in [74], with an emphasis on the need for looking for better suited languages for HPC than the currently used C/C++ and Fortran.

Finally, apart from the aforementioned challenges and based on our analysis in this paper, we identify the following challenges for the types of parallel processing considered in this work:

- (1) Difficulty of offering efficient APIs for hybrid parallel systems includes difficulty of automatic load balancing in hybrid systems. Currently, combinations of APIs with proper optimizations at various parallelization levels are required such as MPI + OpenMP and MPI + OpenMP + CUDA. This stems directly from Figure 1 where there is no single approach/API covering all the configurations in the diagram.

- (2) Few programming environments oriented on several criteria apart from performance. Optimizations using performance and, e.g., energy consumption are performed at the level of algorithms or scheduling

rather than embedded into programming environments or APIs. This suggests the lack of consideration of energy usage in APIs, especially APIs allowing us to obtain desired performance-energy goals for particular classes of applications and compute devices. This is shown in Table 3. This requires automatic tools for determination of performance vs energy profiles for various applications and compute devices.

- (3) Lack of knowledge (of researchers) to integrate various APIs for hybrid systems; many researchers know only single APIs and are not proficient in using all options shown in Table 5.

- (4) Need for benchmarking modern and representative applications on various HPC systems with new hardware features, e.g., latest features of new GPU families such as independent thread scheduling in NVIDIA Volta, memory oversubscription in NVI-DIA Pascal + series cards, cooperative groups, etc. This stems from very fast developments in the APIs which is shown in Table 4.

- (5) Convergence of APIs that target similar environments, e.g., OpenMP and OpenCL. OpenMP now allows offloading to GPUs, accelerators, etc., as shown in Table 3 and some of their applications overlap. This raises a question on whether both will follow in the same direction or diverge more for particular uses.

- (6) Lack of automatic determination of application parameters run on complex parallel systems, especially hybrid systems, i.e., numbers of threads and thread affinity on CPUs, grid configurations on GPUs, load balancing among compute devices, etc. Some works [75] have attempted automation of this process but this field of autotuning in such environments, as also shown above, is relatively undeveloped yet.

- (7) Difficulty in porting of specialized existing parallel programming environments and libraries to modern HPC systems when one wants to use the architectural benefits of the latest hardware. This is also related to the fast changes in the hardware architectures and APIs following these such as for the latest GPU generations and CUDA versions, but also for other APIs, as shown in Table 4.

- (8) Problem of finding best hardware configuration for a given problem and its implementation (CPU/GPU/other accelerators/hybrid), considering relative performance of CPUs, GPUs, interconnects, etc. Certain environments such as MERPSYS [76] allow for simulation of parallel application execution using various hardwares including compute devices such as CPUs and GPUs but the process requires prior calibration on small systems and target applications.

- (9) Lack of standardized APIs for new technologies such as NVRAM in parallel computing. This is related to the technology being very new and starting to be used for HPC, as shown in Section 9.

TABLE 3: Technologies and parallelism.

| Tech/API            | Level of parallelism                                                                                                                                                                                                                                                                                                                                                                     | Parallelism constructs                                                                                                                                                                      | Synchronization constructs                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OpenMP              | Thread teams executing some regions of an application                                                                                                                                                                                                                                                                                                                                    | Directives that define that a certain region is to be executed in parallel, such as #pragma omp parallel, #pragma omp sections, etc.                                                        | Several constructs that allow<br>synchronization such as #pragma omp<br>barrier, constructs that denote that a<br>part of code be executed by a certain<br>thread, e.g., #pragma omp master,<br>#pragma omp single, critical section<br>#pragma omp critical, directives for<br>data synchronization, e.g., #pragma<br>omp atomic                                                                                      |

| CUDA                | Threads executing kernels in parallel, threads are organized into a grid of blocks each of which consists a number of threads, both threads in a block and blocks in a grid can be organized in 1D, 2D, or 3D logical structures, kernel execution, host to device and device to host copying can be overlapped if issued into various CUDA streams                                      | Invocation of a kernel function launches parallel computations by a grid of threads, possible execution on several GPUs in parallel                                                         | Execution of all grid's threads is synchronized after the kernel has completed; on the host side, execution of individual threads in a block is possible with a call tosyncthreads (), atomic functions available for accessing global memory                                                                                                                                                                          |

| OpenCL              | Work items executing kernels in parallel, work items are organized into an NDRange of work groups each of which consists a number of work items, both work items in a work group and work groups in an NDRange can be organized in 1D, 2D, or 3D logical structures, kernel execution, host to device and device to host copying can be overlapped if issued into various command queues | Invocation of a kernel function launches parallel computations by an NDRange of work items, OpenCL allows parallel execution of kernels on various compute devices such as CPUs and GPUs    | Execution of all NDRange's work items is synchronized after the kernel has completed; on the host side, execution of individual work items in a block is possible with a call to barrier with indication whether a local or global memory variable that should be synchronized, synchronization using events is also possible, atomic operations available for synchronization of references to global or local memory |

| Pthreads            | Threads are launched explicitly for execution of a particular function                                                                                                                                                                                                                                                                                                                   | a call to pthread_create () creates a<br>thread for execution of a specific<br>function for which a pointer is passed as<br>a parameter                                                     | Threads can be synchronized by the thread that called pthread_create () by calling pthread_join (), there are mechanisms for synchronization of threads such as mutexes, condition variables with wait pthread_cond_wait () and notify routines, e.g., pthreadcond_signal (), barrier pthread_barrier*(), implicit memory view synchronization among threads upon invocation of selected functions                     |

| OpenACC             | Three levels of parallelism available: execution of gangs, one or more workers within a gang, vector lanes within a worker                                                                                                                                                                                                                                                               | Parallel execution of code within a block<br>marked with #pragma acc parallel,<br>parallel execution of a loop can be<br>specified with #pragma acc loop                                    | For #pragma acc parallel, an implicit barrier is present at the end of the following block, if async is not present, atomic accesses possible with #pragma acc atomic according to documentation [10], the user should not attempt to implement barrier synchronization, critical sections or locks across any of gang, worker, or vector parallelism                                                                  |

| Java<br>Concurrency | Thread inside the same JVM                                                                                                                                                                                                                                                                                                                                                               | The main tread created during the JVM start in main () method is a root of other threads created dynamically using explicit, e.g., new thread (), or implicit constructs, e.g., thread pool | Typical shared memory mechanisms like synchronized sections or guarded blocks                                                                                                                                                                                                                                                                                                                                          |

| TCP/IP              | The whole network nodes                                                                                                                                                                                                                                                                                                                                                                  | Managed manually by adding and configuring hardware                                                                                                                                         | Using IP addresses and ports for distinguishing the connections/ destinations, no specific constructs                                                                                                                                                                                                                                                                                                                  |

| TABLE | 3: | Continued. |

|-------|----|------------|

|       |    |            |