# Introduction to Electronic Design Automation (EDA)

張耀文 原著

Yao-Wen Chang

ywchang@cc.ee.ntu.edu.tw

http://cc.ee.ntu.edu.tw/~ywchang

Graduate Institute of Electronics Engineering

Department of Electrical Engineering

National Taiwan University

Taipei 106, Taiwan

Unit 1

1

#### **Administrative Matters**

- Time/Location: Tuesday 2:20-5:20pm; EE-II 104

- Instructor: Yao-Wen Chang, Chung-Yang Huang, Chien-Mo Li

- E-mail: {ywchang, ric, cmli}@cc.ee.ntu.edu.tw

- URL: http://cc.ee.ntu.edu.tw/~eda/Course/IntroEDA06

- Office: BL-428; EE-II 444; EE-II 339

- Office Hours: Contact Instructors

- Teaching Assistants

- \_ TBD

- Prerequisites: Computer Programming & logic design.

- Required Text: S. H. Gerez, Algorithms for VLSI Design Automation, John Wiley & Sons, 1999.

- **References:** Cormen, Leiserson, and Rivest, *Introduction to Algorithms*, 2<sup>nd</sup> Ed., McGraw Hill/MIT Press, 2001.

- Other supplementary reading materials will be provided.

## **Course Objectives**

- Study techniques for electronic design automation (EDA), a.k.a. computer-aided design (CAD).

- Study IC technology evolution and their impacts on the development of EDA tools

- Study problem-solving (-finding) techniques!!!

Unit 1 NTUEE / Intro. EDA 3

#### **Course Contents**

- Introduction to VLSI design flow/styles/automation, technology roadmap, and CMOS Technology

- Algorithmic graph theory

- Computational Complexity and Optimization

- Physical design: partitioning, floorplanning, placement, routing, compaction, deep submicron effects

- Logic synthesis and verification

- (High Level Synthesis)

- Simulation

- Testing

# **Grading Policy**

#### Grading Policy:

– Homework assignments: 25%

Midterm Exam :20%

Programming assignment: 25%

Final Exam: 30%

Homework: 50% per day late penalty

Due dates on web

• Academic Honesty: Avoiding cheating at all cost.

Unit 1 NTUEE / Intro. EDA 5

#### **Unit 1: Introduction**

- Course contents:

- Introduction to VLSI design flow/methodologies/styles

- Introduction to VLSI design automation tools

- Semiconductor technology roadmap

- CMOS technology

- Readings

- \_ Chapters 1-2

- Appendix A

# **Milestones for IC Industry**

- 1947: Bardeen, Brattain & Shockly invented the transistor, foundation of the IC industry.

- 1952: SONY introduced the first transistor-based radio.

- 1958: Kilby invented integrated circuits (ICs).

- 1965: Moore's law.

- 1968: Noyce and Moore founded Intel.

- 1970: Intel introduced 1 K DRAM.

Vacuum tube

Unit 1

In 1956 John Bardeen, William Shockley and Walter Brattain shared the Nobel Prize in Physics for their discovery of the transistor. Bardeen, Shockly,

**Brattain**

**First transistor**

First IC by Noyce

First IC by Kilby

NTUEE / Intro. EDA

.

## **Milestones for IC Industry**

- 1971: Intel announced 4-bit 4004 microprocessors (2250 transistors).

- 1976/81: Apple II/IBM PC (technology driver).

- 1984: Xilinx invented FPGA's.

- 1985: Intel began focusing on microprocessor products.

- 1987: TSMC was founded (fabless IC design).

- 1991: ARM introduced its first embeddable RISC IP core (chipless IC design).

Intel founders

4004

**IBM PC**

8

Unit 1 NTUEE / Intro. EDA

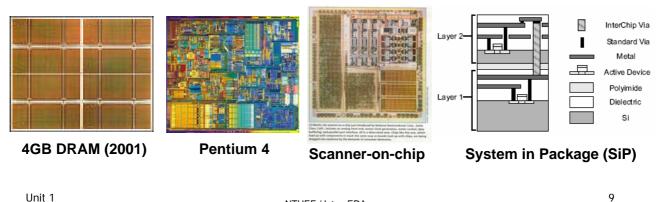

# Milestones for IC Industry (Cont'd)

- 1996: Samsung introduced IG DRAM.

- 1998: IBM announces1GHz experimental microprocessor.

- 1999/earlier: System-on-Chip (SoC) applications.

- 2002/earlier: System-in-Package (SiP) technology.

- An Intel P4 processor contains 42 million transistors (1 billion in 2005)

- Today, we produce > 30 million transistors per person (1 billion/person by 2008).

Unit 1 NTUEE / Intro. EDA

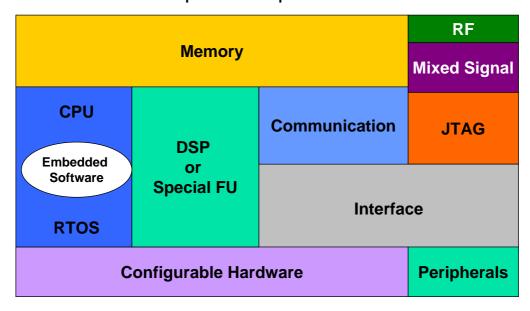

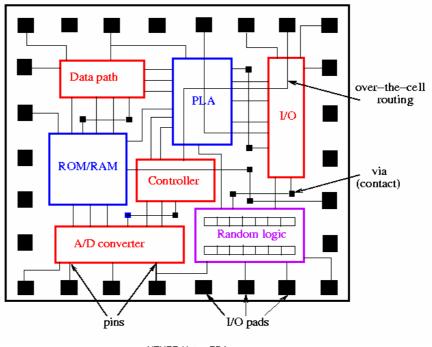

#### **SoC Architecture**

An SoC system typically consists of a collection of components/subsystems that are appropriately interconnected to perform specified functions for users.

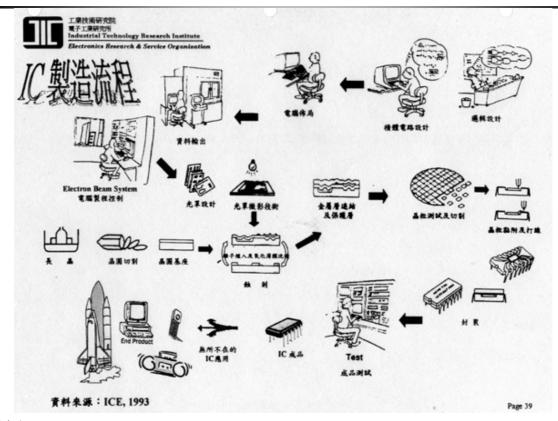

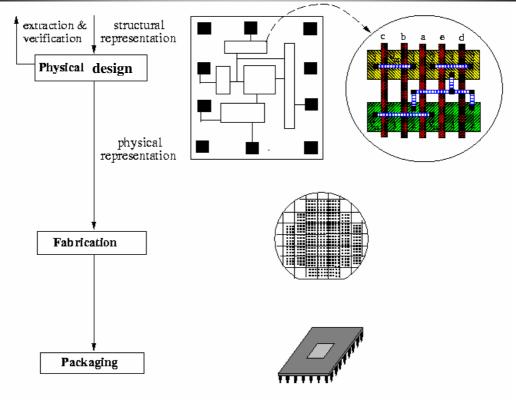

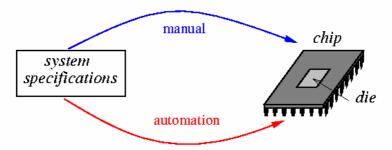

# **IC Design & Manufacturing Process**

Unit 1 NTUEE / Intro. EDA 11

# From Wafer to Chip

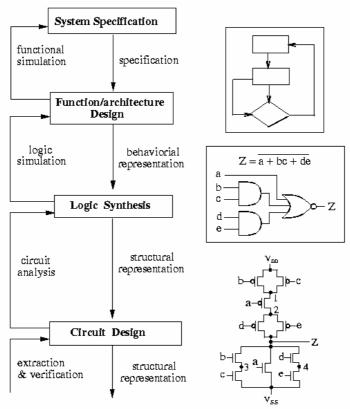

# **Traditional VLSI Design Cycles**

- 1. System specification

- 2. Functional design

- 3. Logic synthesis

- 4. Circuit design

- 5. Physical design and verification

- 6. Fabrication

- 7. Packaging

- Other tasks involved: testing, simulation, etc.

- Design metrics: area, speed, power dissipation, noise, design time, testability, etc.

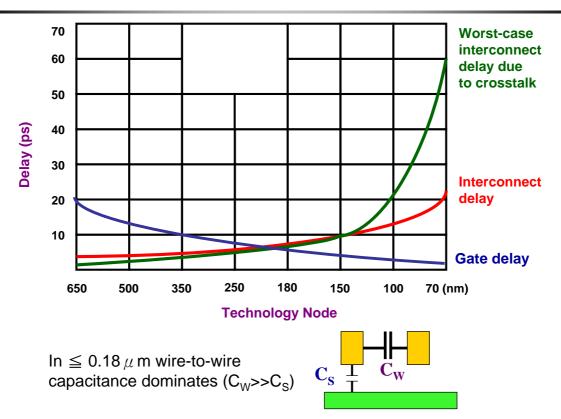

- Design revolution: interconnect (not gate) delay dominates circuit performance in deep submicron era.

- Interconnects are determined in physical design.

- Shall consider interconnections in early design stages.

Unit 1 NTUEE / Intro. EDA

## **Traditional VLSI Design Cycle**

## Traditional VLSI Design Flow (Cont'd)

Unit 1 NTUEE / Intro. EDA 15

## **Design Actions**

- **Synthesis:** increasing information about the design by providing more detail (e.g., logic synthesis, physical synthesis).

- Analysis: collecting information on the quality of the design (e.g., timing analysis).

- **Verification:** checking whether a synthesis step has left the specification intact (e.g., layout verification).

- Optimization: increasing the quality of the design by rearrangements in a given description (e.g., logic optimizer, timing optimizer).

- Design Management: storage of design data, cooperation between tools, design flow, etc. (e.g., database).

## **Design Issues and Tools**

- System-level design

- Partitioning into hardware and software, co-design, co-simulation, etc.

- Cost estimation, design-space exploration

- Algorithmic-level design

- Behavioral descriptions (e.g., in Verilog, VHDL)

- High-level simulation

- From algorithms to hardware modules

- High-level (or architectural) synthesis

- Logic design:

- Schematic entry

- Register-transfer level and logic synthesis

- Gate-level simulation (functionality, power, etc.)

- Timing analysis

- Formal verification

Unit 1 NTUEE / Intro. EDA 17

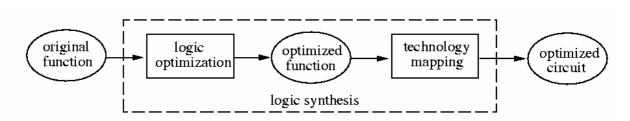

## Logic Design/Synthesis

- Logic synthesis programs transform Boolean expressions into logic gate networks in a particular library.

- Optimization goals: minimize area, delay, power, etc

- Technology-independent optimization: logic optimization

- Optimizes Boolean expression equivalent.

- Technology-dependent optimization: technology mapping/library binding

- Maps Boolean expressions into a particular cell library.

## **Logic Optimization Examples**

- Two-level: minimize the # of product terms.

- $F = \bar{x_1}\bar{x_2}\bar{x_3} + \bar{x_1}\bar{x_2}x_3 + x_1\bar{x_2}\bar{x_3} + x_1\bar{x_2}x_3 + x_1x_2\bar{x_3} \Rightarrow F = \bar{x_2} + x_1\bar{x_3}.$

- Multi-level: minimize the #'s of literals, variables.

- E.g., equations are optimized using a smaller number of literals.

Methods/CAD tools: Quine-McCluskey method (exponential-time exact algorithm), Espresso (heuristics for two-level logic), MIS (heuristics for multi-level logic), Synopsys, etc.

Unit 1 NTUEE / Intro. EDA 19

# **Design Issues and Tools (Cont'd)**

- Transistor-level design

- Switch-level simulation

- Circuit simulation

- Physical (layout) design

- Partitioning

- Floorplanning and Placement

- Routing

- Layout editing and compaction

- Design-rule checking

- Layout extraction

- Design management

- Data bases, frameworks, etc.

- Silicon compilation: from algorithm to mask patterns

- The *idea* is approached more and more, but still far away from a single *push-buttom* operation

# Circuit Simulation of a CMOS Inverter (0.6 $\mu$ m)

M1 3 2 0 0 nch W=1.2u L=0.6u AS=2.16p PS=4.8u AD=2.16p PD=4.8u M2 3 2 1 1 pch W=1.8u L=0.6u AS=3.24p PS=5.4u AD=3.24p PD=5.4u CL 3 0 0.2pF VDD 1 0 3.3 VIN 2 0 DC 0 PULSE (0 3.3 Ons 100ps 100ps 2.4ns 5ns) .LIB '../mod\_06' typical .OPTION NOMOD POST INGOLD=2 NUMDGT=6 BRIEF .DC VIN OV 3.3V 0.001V .PRINT DC V(3) .TRAN 0.001N 5N .PRINT TRAN V(2) V(3) .END  $v_{out}$  2 ns Time Unit 1 21

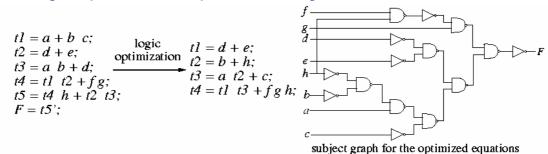

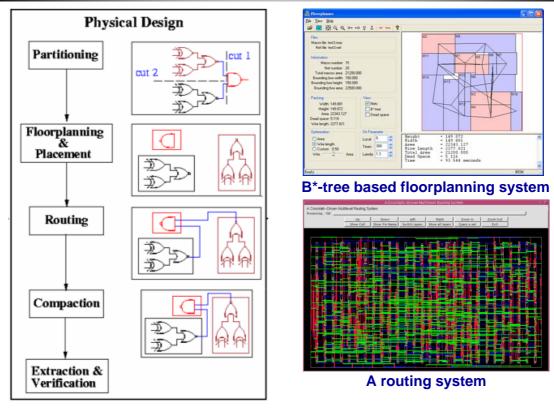

# **Physical Design**

NTUEE / Intro. EDA

- Physical design converts a circuit description into a geometric description.

- The description is used to manufacture a chip.

- Physical design cycle:

- 1. Logic partitioning

- 2. Floorplanning and placement

- 3. Routing

- 4. Compaction

- Others: circuit extraction, timing verification and design rule checking

# **Physical Design Flow**

Unit 1 23 NTUEE / Intro. EDA

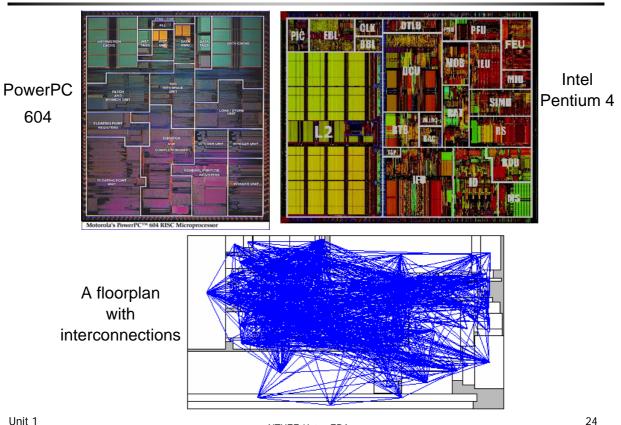

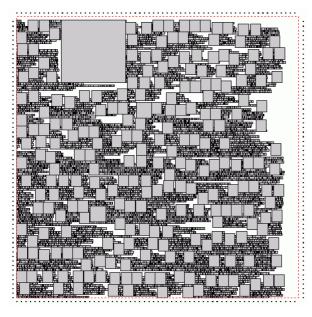

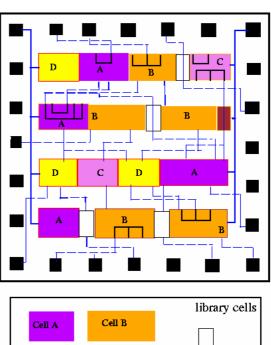

# **Floorplan Examples**

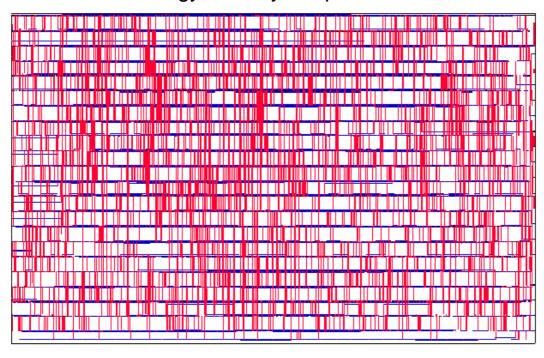

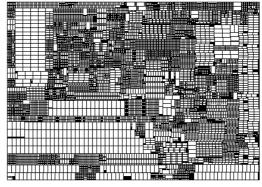

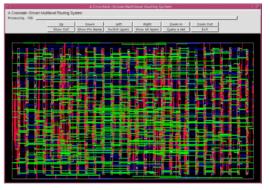

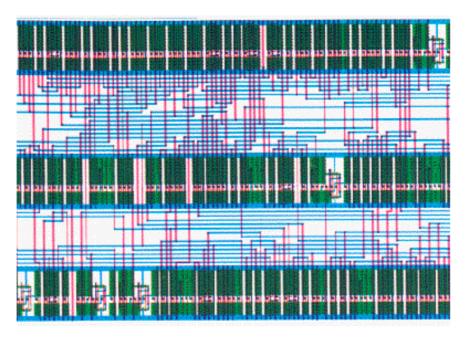

# **Routing Example**

• 0.18um technology, two layers, pitch = 1 um, 8109 nets.

Unit 1 NTUEE / Intro. EDA 25

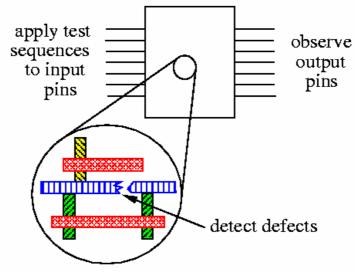

# **Testing**

- Goal of testing is to ensure defect-free products.

- Need high quality tests that can detect realistic defects

- Varieties of testing: functional testing, performance testing

26

# **IC Design Considerations**

- Several conflicting considerations:

- Design Complexity: large number of devices/transistors

- Performance: optimization requirements for high performance

- Time-to-market: about a 15% gain for early birds

- Cost: die area, packaging, testing, etc.

- Others: power, signal integrity (noise, etc.), testability, reliability, manufacturability, etc.

Unit 1 NTUEE / Intro. EDA 27

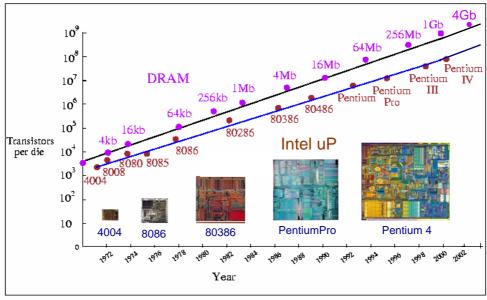

## "Moore's" Law: Driving Technology Advances

- Logic capacity doubles per IC at a regular interval.

- Moore: Logic capacity doubles per IC every two years (1975).

- D. House: Computer performance doubles every 18 months (1975)

# **Technology Roadmap for Semiconductors**

| Year                    | 1997    | 1999    | 2002    | 2005    | 2008    | 2011    | 2014      |

|-------------------------|---------|---------|---------|---------|---------|---------|-----------|

| Technology              |         |         |         |         |         |         |           |

| node $(nm)$             | 250     | 180     | 130     | 100     | 70      | 50      | 35        |

| On-chip local           |         |         |         |         |         |         |           |

| clock $(GHz)$           | 0.75    | 1.25    | 2.1     | 3.5     | 6.0     | 10      | 16.9      |

| Microprocessor          |         |         |         |         |         |         |           |

| chip size $(mm^2)$      | 300     | 340     | 430     | 520     | 620     | 750     | 901       |

| Microprocessor          |         |         |         |         |         |         |           |

| transistors/chip        | 11M     | 21M     | 76M     | 200M    | 520M    | 1.40B   | 3.62B     |

| Microprocessor          |         |         |         |         |         |         |           |

| cost/transistor         | 3000    | 1735    | 580     | 255     | 110     | 49      | 22        |

| (×10 <sup>-8</sup> USD) |         |         |         |         |         |         |           |

| DRAM bits               |         |         |         |         |         |         |           |

| per chip                | 256M    | 1G      | 4G      | 16G     | 64G     | 256G    | 1T        |

| Wiring level            | 6       | 6–7     | 7       | 7-8     | 8–9     | 9       | 10        |

| Supply voltage          |         |         |         |         |         |         |           |

| (V)                     | 1.8-2.5 | 1.5-1.8 | 1.2-1.5 | 0.9-1.2 | 0.6-0.9 | 0.5-0.6 | 0.37-0.42 |

| Power (W)               | 70      | 90      | 130     | 160     | 170     | 175     | 183       |

- Source: International Technology Roadmap for Semiconductors (ITRS), Nov. 2001. <a href="http://www.itrs.net/ntrs/publntrs.nsf">http://www.itrs.net/ntrs/publntrs.nsf</a>.

- Deep submicron technology: node (**feature size**) < 0.25  $\mu$ m.

- Nanometer Technology: node < 0.1 μm.

Unit 1 NTUEE / Intro. EDA 29

# ITRS 2004 Technology Roadmap

|     | Year of Production                                                                             | 2003       | 2004       | 2005       | 2006       | 2007       | 2008       | 2009        |

|-----|------------------------------------------------------------------------------------------------|------------|------------|------------|------------|------------|------------|-------------|

|     | Technology Node                                                                                |            | hp90       |            |            | hp65       |            |             |

|     | DRAM ½ Pitch (nm)                                                                              | 100        | 90         | 80         | 70         | 65         | 57         | 50          |

|     | MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                                             | 120        | 107        | 95         | 85         | 76         | 67         | 60          |

|     | MPU/ASIC 1/2 Pitch (nm) (Un-contacted Poly)                                                    | 107        | 90         | 80         | 70         | 65         | 57         | 50          |

|     | MPU Printed Gate Length (nm) ††                                                                | 65         | 53         | 45         | 40         | 35         | 32         | 28          |

|     | MPU Physical Gate Length (nm)                                                                  | 45         | 37         | 32         | 28         | 25         | 22         | 20          |

|     | SRAM Cell (6-transistor) Area factor ++                                                        | 120.3      | 117.8      | 115.6      | 113.7      | 111.9      | 110.4      | 109         |

|     | Logic Gate (4-transistor) Area factor ++                                                       | 320        | 320        | 320        | 320        | 320        | 320        | 320         |

|     | SRAM Cell (6-transistor) Area efficiency ++                                                    | 0.63       | 0.63       | 0.63       | 0.63       | 0.63       | 0.63       | 0.63        |

|     | Logic Gate (4-transistor) Area efficiency ++                                                   | 0.50       | 0.50       | 0.50       | 0.50       | 0.50       | 0.50       | 0.50        |

| NEW | SRAM Cell (6-transistor) Area ++                                                               | 1.23       | 0.95       | 0.74       | 0.58       | 0.45       | 0.35       | 0.28        |

|     | SRAM Cell (6-transistor) Area w/overhead ++                                                    | 2.0        | 1.5        | 1.2        | 0.93       | 0.73       | 0.57       | 0.45        |

| NEW | Logic Gate (4-transistor) Area ++                                                              | 3.27       | 2.59       | 2.06       | 1.63       | 1.30       | 1.03       | 0.82        |

|     | Logic Gate (4-transistor) Area w/overhead ++                                                   | 6.5        | 5.2        | 4.1        | 3.3        | 2.6        | 2.1        | 1.6         |

|     | Transistor density SRAM (Mtransistors/cm <sup>2</sup> )                                        | 305        | 393        | 504        | 646        | 827        | 1,057      | 1,348       |

|     | Transistor density logic (Mtransistors/cm²)                                                    | 61         | 77         | 97         | 122        | 154        | 194        | 245         |

|     | Generation at introduction *                                                                   |            | р07с       |            |            | p10c       |            |             |

| WAS | Functions per chip at introduction (million transistors [Mtransistors])                        | 180        | 226        | 285        | 360        | 453        | 571        | 719         |

| IS  | Functions per chip at introduction (million transistors [Mtransistors])                        | <u>307</u> | <u>386</u> | <u>487</u> | <u>614</u> | <u>773</u> | <u>974</u> | <u>1227</u> |

|     | Chip size at introduction (mm²) ‡                                                              | 280        | 280        | 280        | 280        | 280        | 280        | 280         |

|     | Cost performance MPU (Mtransistors/cm <sup>2</sup> at introduction) (including on-chip SRAM) ‡ | 110        | 138        | 174        | 219        | 276        | 348        | 438         |

|     | Generation at production *                                                                     |            | p04c       |            |            | р07с       |            |             |

|     | Functions per chip at production (million transistors [Mtransistors])                          | 153        | 193        | 243        | 307        | 386        | 487        | 614         |

|     | Chip size at production (mm²) §§                                                               | 140        | 140        | 140        | 140        | 140        | 140        | 140         |

|     | Cost performance MPU (Mtransistors/cm <sup>2</sup> at<br>production, including on-chip SRAM) ‡ | 110        | 138        | 174        | 219        | 276        | 348        | 438         |

# ITRS 2004 Technology Roadmap (cont'd)

|     | Year of Production                                                                                   | 2010         | 2011         | 2012         | 2013  | 2014         | 2015         | 2016         | 2017         | 2018         |

|-----|------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|-------|--------------|--------------|--------------|--------------|--------------|

|     | Technology Node                                                                                      | hp45         |              |              | hp32  |              |              | hp22         |              |              |

| WAS | DRAM ½ Pitch (nm)                                                                                    | 45           |              | 35           | 32    |              | 25           | 22           |              | 18           |

| IS  | DRAM ½ Pitch (nm)                                                                                    | 45           | <u>40</u>    | 35           | 32    | <u>28</u>    | 25           | 22           | <u>20</u>    | 18           |

| WAS | Generation at introduction *                                                                         | p13c         |              |              | p16c  |              |              | р19с         |              |              |

| IS  | Generation at introduction *                                                                         | p13c         | _=           |              | p16c  | _==          |              | p19c         | _=           |              |

| WAS | Functions per chip at introduction (million transistors [Mtransistors])                              | 1,546        |              | 2,454        | 3,092 |              | 4,908        | 6,184        |              | 9,816        |

| IS  | Functions per chip at introduction (million transistors [Mtransistors])                              | <u>1,546</u> | <u>1,948</u> | <u>2,454</u> | 3,092 | <u>3,896</u> | <u>4,908</u> | <u>6,184</u> | <u>7,791</u> | <u>9.816</u> |

| WAS | Chip size at introduction (mm²) ‡                                                                    | 280          |              | 280          | 280   |              | 280          | 280          |              | 280          |

| IS  | Chip size at introduction (mm²) ‡                                                                    | 280          | 280          | 280          | 280   | 280          | 280          | 280          | 280          | 280          |

| WAS | Cost performance MPU (Mtransistors/cm <sup>2</sup><br>at introduction) (including on-chip SRAM)<br>‡ | 552          |              | 876          | 1,104 |              | 1,753        | 2,209        |              | 3,506        |

| IS  | Cost performance MPU (Mtransistors/cm <sup>2</sup><br>at introduction) (including on-chip SRAM)<br>‡ | 552          | <u>696</u>   | 876          | 1,104 | <u>1,391</u> | 1,753        | 2,209        | <u>2,783</u> | 3,506        |

| WAS | Generation at production *                                                                           | p10c         |              |              | p13c  |              |              | p16c         |              |              |

| IS  | Generation at production *                                                                           | p10c         | _==          |              | p13c  | _==          |              | p16c         | _==          |              |

| WAS | Functions per chip at production (million<br>transistors [Mtransistors])                             | 773          |              | 1,227        | 1,546 |              | 2,454        | 3,092        |              | 4,908        |

| IS  | Functions per chip at production (million transistors [Mtransistors])                                | 773          | <u>974</u>   | 1,227        | 1,546 | <u>1,948</u> | 2,454        | 3,092        | 3,896        | 4,908        |

| WAS | Chip size at production (mm²) §§                                                                     | 140          |              | 140          | 140   |              | 140          | 140          |              | 140          |

| IS  | Chip size at production (mm²) §§                                                                     | 140          | <u>140</u>   | 140          | 140   | <u>140</u>   | 140          | 140          | <u>140</u>   | 140          |

| WAS | Cost performance MPU (Mtransistors/cm <sup>2</sup><br>at production, including on-chip SRAM) ‡       | 552          |              | 876          | 1,104 |              | 1,753        | 2,209        |              | 3,506        |

| IS  | Cost performance MPU (Mtransistors/cm <sup>2</sup><br>at production, including on-chip SRAM) ‡       | 552          | <u>696</u>   | 876          | 1,104 | <u>1,391</u> | 1,753        | 2,209        | 2,783        | 3,506        |

Unit 1 NTUEE / Intro. EDA 31

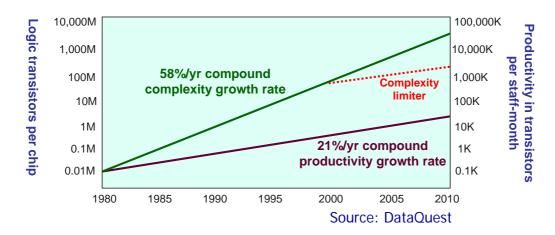

# **Design Complexity Increases Dramatically!!**

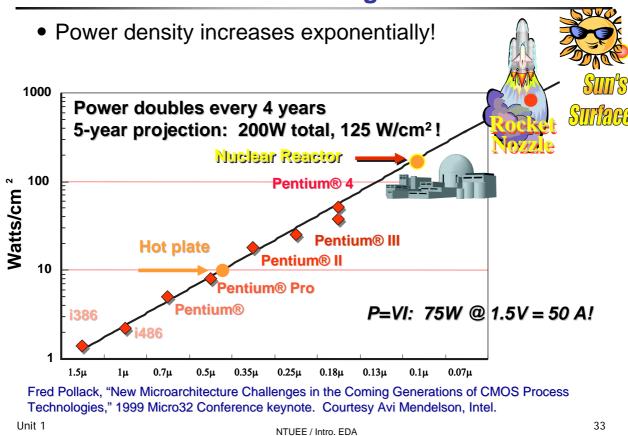

# **Power Is Another Big Problem!!**

#### **Interconnect Dominates Circuit Performance!!**

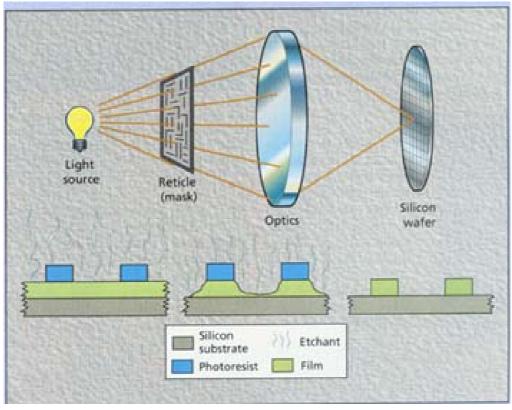

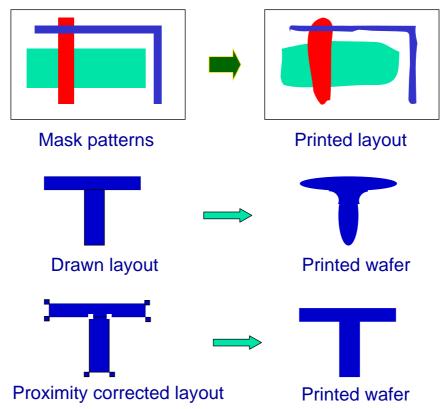

# **Lithography Process**

Unit 1 NTUEE / Intro. EDA 35

# **Sub-wavelength Lithography Causes Problems!!**

Unit 1 NTUEE / Intro. EDA 36

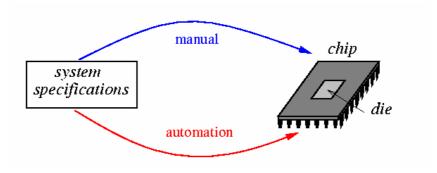

# **Design Productivity Crisis**

- Human factors may limit design more than technology.

- Keys to solve the productivity crisis: CAD (tool & methodology), hierarchical design, abstraction, IP reuse, platform-based design, etc.

Unit 1 NTUEE / Intro. EDA 37

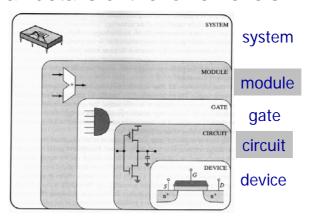

## **Hierarchical Design**

- *Hierarchy:* something is composed of simpler things.

- Design cannot be done in one step ⇒ partition the design hierarchically.

#### **Abstraction**

• Abstraction: when looking at a certain level, you don't need to know all details of the lower levels.

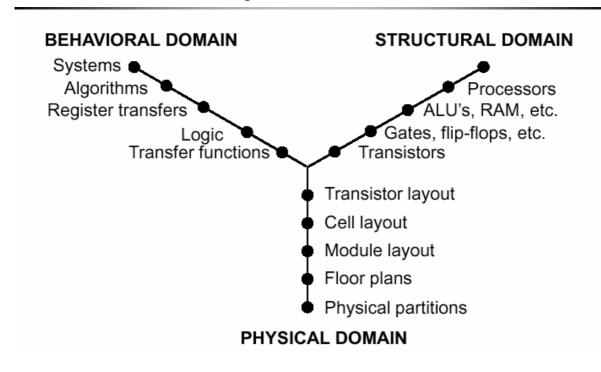

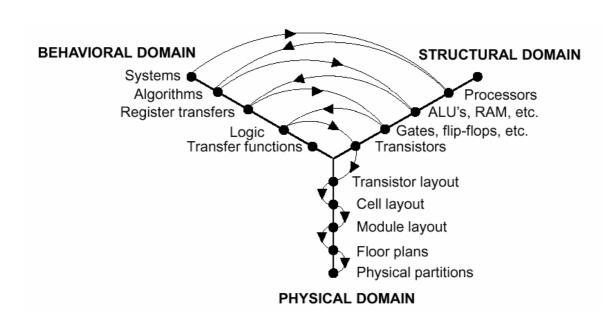

- Design domains:

- Behavioral: black box view

- Structural: interconnection of subblocks

- Physical: layout properties

- Each design domain has its own hierarchy.

Unit 1 NTUEE / Intro. EDA 39

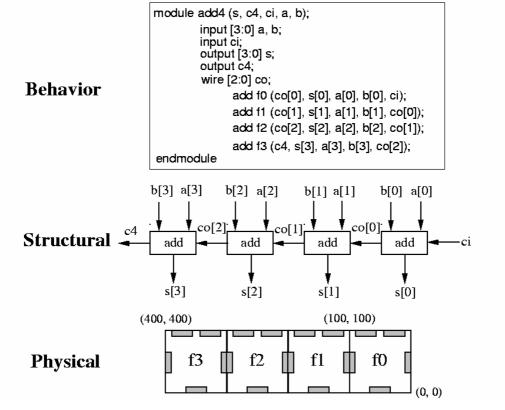

#### **Three Design Views**

Unit 1 NTUEE / Intro. EDA 40

# Gajski's Y-Chart

Unit 1 NTUEE / Intro. EDA 41

# **Top-Down Structural Design**

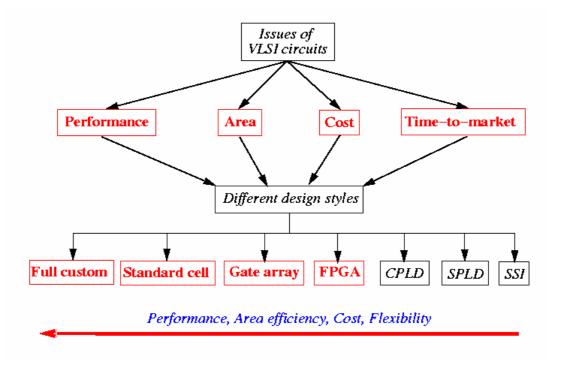

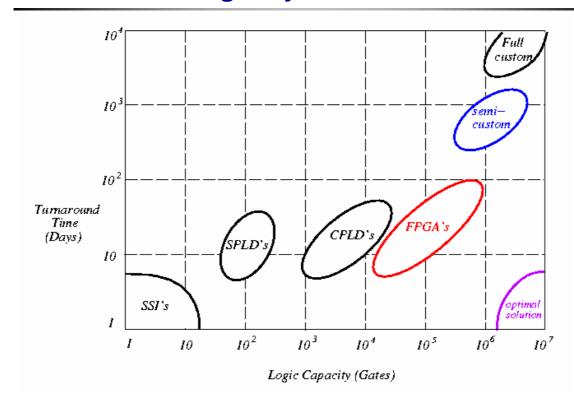

# **Design Styles**

• Specific design styles shall require specific CAD tools

Unit 1 NTUEE / Intro. EDA 43

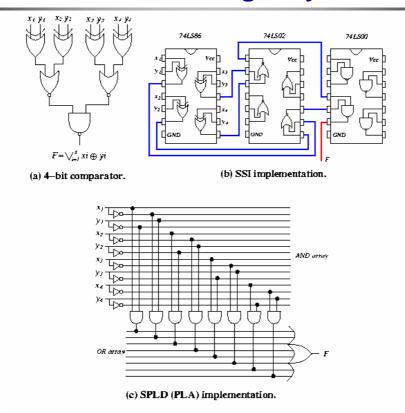

# SSI/SPLD Design Style

# **Full Custom Design Style**

- Designers can control the shape of all mask patterns.

- Designers can specify the design up to the level of individual transistors.

Unit 1 45 NTUEE / Intro. EDA

# **Standard Cell Design Style**

- Selects pre-designed cells (of the same height) to implement logic

- Over-the-cell routing is pervasive in modern designs

# **Standard Cell Example**

Courtesy of Newton/Pister, UC-Berkeley

Unit 1 NTUEE / Intro. EDA 47

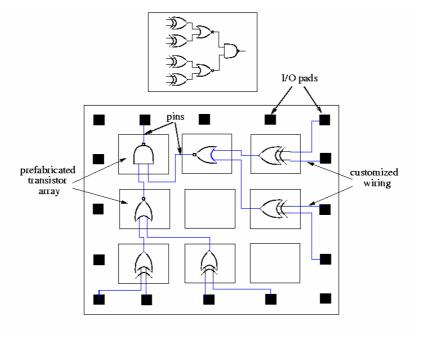

# **Gate Array Design Style**

- Prefabricates a transistor array

- Needs wiring customization to implement logic

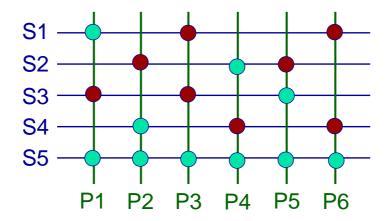

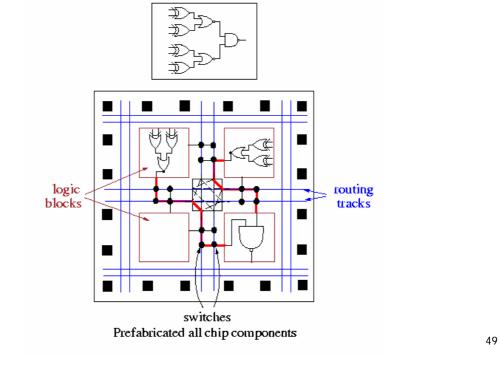

# **FPGA Design Style**

- Logic and interconnects are both prefabricated.

- Illustrated by a symmetric array-based FPGA

# **Array-Based FPGA Example**

Unit 1

Lucent Technologies 15K ORCA FPGA, 1995

- 0.5 um 3LM CMOS

- 2.45 M Transistors

- 1600 Flip-flops

- 25K bit user RAM

- 320 I/Os

Fujitsu's non-volatile Dynamically Programmable Gate Array (DPGA), 2002

Unit 1 NTUEE / Intro. EDA 50

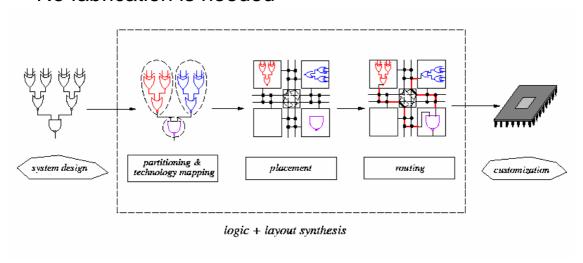

# **FPGA Design Process**

- Illustrated by a symmetric array-based FPGA

- No fabrication is needed

Unit 1 NTUEE / Intro. EDA 51

# **Comparisons of Design Styles**

|                  | Full<br>custom | Standard<br>cell | Gate<br>array | FPGA         | SPLD         |

|------------------|----------------|------------------|---------------|--------------|--------------|

| Cell size        | variable       | fixed height*    | fixed         | fixed        | fixed        |

| Cell type        | variable       | variable         | fixed         | programmable | programmable |

| Cell placement   | variable       | in row           | fixed         | fixed        | fixed        |

| Interconnections | variable       | variable         | variable      | programmable | programmable |

<sup>\*</sup> Uneven height cells are also used.

|                               | Full<br>custom | Standard<br>cell | Gate<br>array | FPGA | SPLD |

|-------------------------------|----------------|------------------|---------------|------|------|

| Fabrication time              |                |                  | +             | +++  | ++   |

| Packing density               | +++            | ++               | +             |      |      |

| Unit cost in large quantity   | +++            | ++               | +             |      | _    |

| Unit cost in small quantity   |                |                  | +             | +++  | ++   |

| Easy design and simulation    |                |                  | _             | ++   | +    |

| Easy design change            |                |                  | _             | ++   | ++   |

| Accuracy of timing simulation | _              | _                | _             | +    | ++   |

| Chip speed                    | +++            | ++               | +             | _    |      |

+ desirable; - not desirable

# **Design Style Trade-offs**

Unit 1 NTUEE / Intro. EDA 53

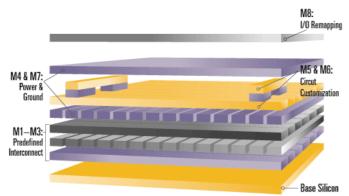

# The Structured ASIC Is Coming!

- A structured ASIC consists of predefined metal and via layers, as well as a few of them for customization.

- The predefined layers support power distribution and local communications among the building blocks of the device.

- Advantages: fewer masks (lower cost); easier physical extraction and analysis.

A structured ASIC (M5 & M6 can be customized)

Faraday's 3MPCA structured ASIC (M4--M6 can be customized)

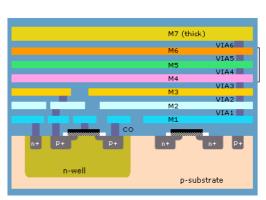

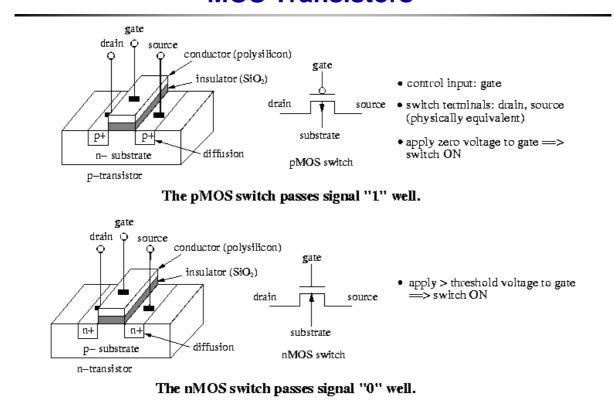

# **MOS Transistors**

Unit 1 NTUEE / Intro. EDA 55

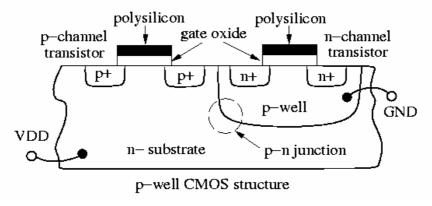

# **Complementary MOS (CMOS)**

- The most popular VLSI technology (vs. BiCMOS, nMOS).

- CMOS uses both *n*-channel and *p*-channel transistors.

- Advantages: lower power dissipation, higher regularity, more reliable performance, higher noise margin, larger fanout, etc.

- Each type of transistor must sit in a material of the complementary type (the reverse-biased diodes prevent unwanted current flow).

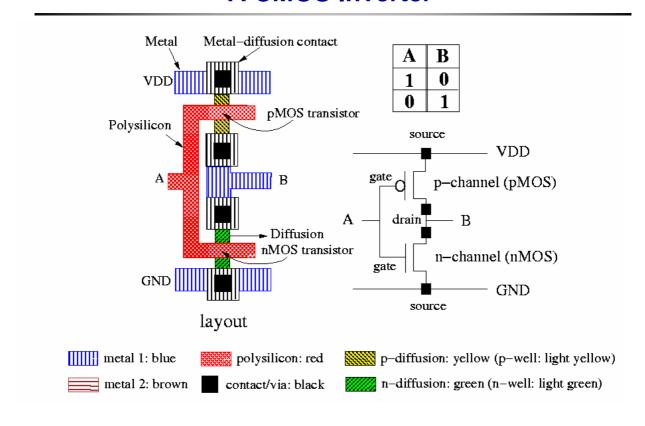

## **A CMOS Inverter**

Unit 1 NTUEE / Intro. EDA 57

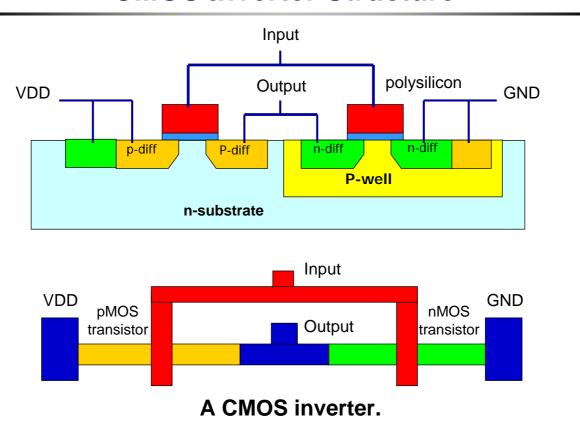

# **CMOS Inverter Structure**

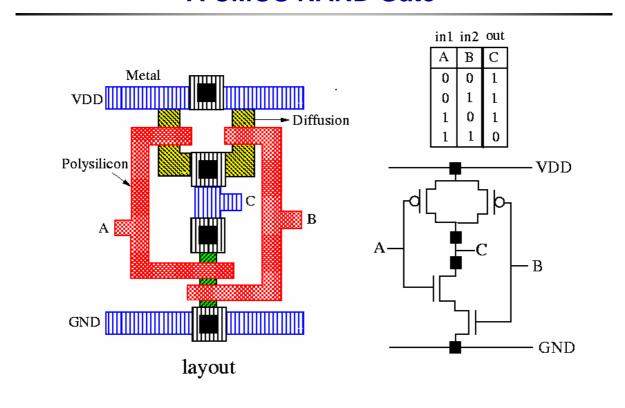

# **A CMOS NAND Gate**

Unit 1 NTUEE / Intro. EDA 59

# **A CMOS NOR Gate**

# **Basic CMOS Logic Library**

| Name                            | Distinctive<br>shape | Algebraic equation       | Cost (# of<br>transistors) | Scaled gate<br>delay (ps) |

|---------------------------------|----------------------|--------------------------|----------------------------|---------------------------|

| AND                             | х<br>ү —             | F=XY                     | 6                          | 24                        |

| OR                              | х<br>ү ——            | F=X+Y                    | 6                          | 24                        |

| NOT<br>(inverter/<br>repeater)  | х                    | F=X                      | 2                          | 10                        |

| Buffer<br>(driver/<br>repeater) | x                    | F=X                      | 4                          | 20                        |

| NAND                            | х                    | F=XY                     | 4                          | 14                        |

| NOR                             | х                    | F= <del>X+Y</del>        | 4                          | 14                        |

| Exclusive-OR (XOR)              | х<br>ч               | F=XY+XY<br>=X <b>Q</b> Y | 14                         | 42                        |

Unit 1 NTUEE / Intro. EDA 61

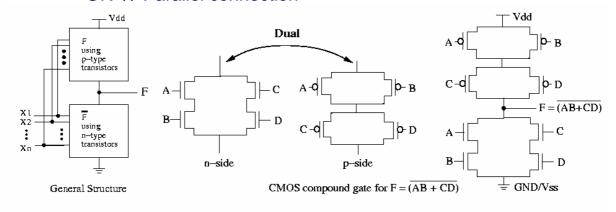

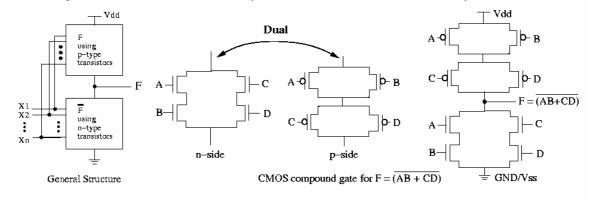

# **Construction of Compound Gates**

- Example:  $F = \overline{A \cdot B + C \cdot D}$ .

- Step 1 (n-network): Invert F to derive n-network  $(\overline{F} = A \cdot B + C \cdot D)$

- Step 2 (n-network): Make connections of transistors:

- AND ⇔ Series connection

- OR ⇔ Parallel connection

# **Construction of Compound Gates (cont'd)**

- Step 3 (p-network): Expand F to derive p-network

- $(F = \overline{AB + CD} = \overline{AB} \cdot \overline{CD} = (\overline{A} + \overline{B}) \cdot (\overline{C} + \overline{D}))$

- each input is inverted

- Step 4 (p-network): Make connections of transistors (same as Step 2).

- Step 5: Connect the *n*-network to GND (typically, 0V) and the *p*-network to VDD (5V, 3.3V, or 2.5V, etc).

Unit 1 NTUEE / Intro. EDA 63

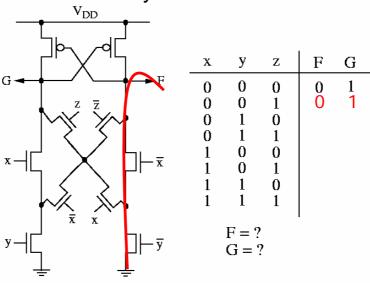

## **A Complex CMOS Gate**

- The functions realized by the n and p networks must be complementary, and one of the networks must conduct for every input combination.

- Duality is not necessary.

Unit 1 NTUEE / Intro. EDA 64

## **CMOS Properties**

- There is always a path from one supply (VDD or GND) to the output.

- There is never a path from one supply to the other. (This is the basis for the low power dissipation in CMOS--virtually no static power dissipation.)

- There is a momentary drain of current (and thus power consumption) when the gate switches from one state to another.

- Thus, CMOS circuits have dynamic power dissipation.

- The amount of power depends on the switching frequency.

Unit 1 NTUEE / Intro. EDA 65

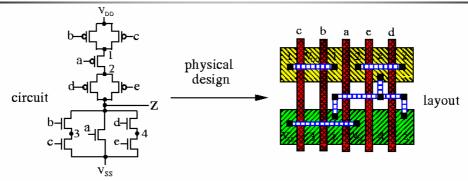

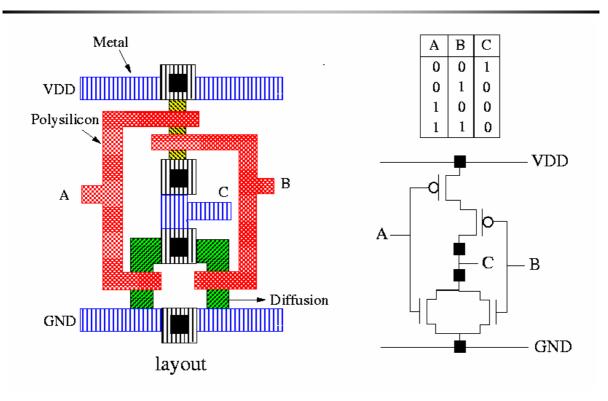

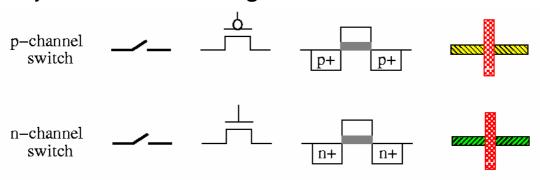

#### **Stick Diagram**

- Intermediate representation between the transistor level and the mask (layout) level.

- Gives topological information (identifies different layers and their relationship)

- Assumes that wires have no width.

- Possible to translate stick diagram automatically to layout with correct design rules.

# Stick Diagram (cont'd)

• When the same materials (on the same layer) touch or cross, they are connected and belong to the same electrical node.

- When **polysilicon** crosses N or P **diffusion**, an N or P transistor is formed.

- Polysilicon is drawn on top of diffusion.

- Diffusion must be drawn connecting the source and the drain.

- Gate is automatically self-aligned during fabrication.

When a metal line needs to be connected to one of the other three conductors, a contact cut (via) is required.

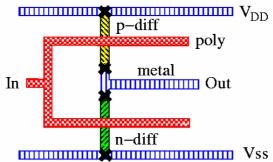

## **CMOS Inverter Stick Diagrams**

Basic layout

More area efficient layout

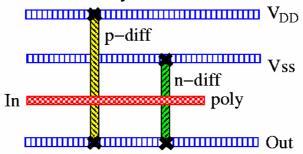

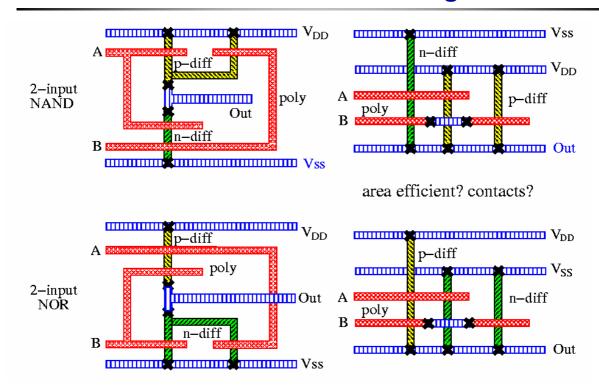

## **CMOS NAND/NOR Stick Diagrams**

Unit 1 NTUEE / Intro. EDA 69

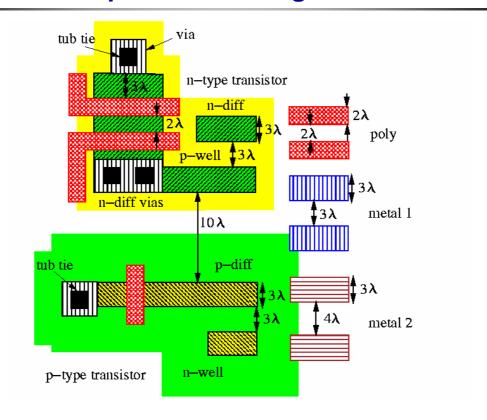

#### **Design Rules**

- Layout rules are used for preparing the masks for fabrication.

- Fabrication processes have inherent limitations in accuracy.

- Design rules specify geometry of masks to optimize yield and reliability (trade-offs: area, yield, reliability).

- Three major rules:

- Wire width: Minimum dimension associated with a given feature.

- Wire separation: Allowable separation.

- Contact: overlap rules.

- Two major approaches:

- "Micron" rules: stated at micron resolution.

- λ rules: simplified micron rules with limited scaling attributes.

- λ may be viewed as the size of minimum feature.

- Design rules represent a tolerance which insures very high probability of correct fabrication (not a hard boundary between correct and incorrect fabrication).

- Design rules are determined by experience.

# **Example CMOS Design Rules**

Unit 1 NTUEE / Intro. EDA 71

# **MOSIS Layout Design Rules**

- MOSIS design rules (SCMOS rules) are available at http://www.mosis.org.

- 3 basic design rules: wire width, wire separation, contact rule.

- MOSIS design rule examples

| R1  | Min active area width                  | 3 λ |

|-----|----------------------------------------|-----|

| R3  | Min poly width                         | 2 λ |

| R4  | Min poly spacing                       | 2 λ |

| R5  | Min gate extension of poly over active | 2 λ |

| R8  | Min metal width                        | 3 λ |

| R9  | Min metal spacing                      | 3 λ |

| R10 | Poly contact size                      | 2 λ |

| R11 | Min poly contact spacing               | 2 λ |