# Selective area growth of germanium and germanium/silicon-germanium quantum wells in silicon waveguides for on-chip optical interconnect applications

S. A. Claussen,\* K. C. Balram, E. T. Fei, T. I. Kamins, J. S. Harris, and D. A. B. Miller

Department of Electrical Engineering, Stanford University, 350 Serra Mall, Stanford, CA 94305, USA \*stephanie.ann.claussen@gmail.com

**Abstract:** We propose a robust fabrication process for growing Ge and Gebased heterostructures in growth windows with Si sidewalls which can be applied to growth in thick Si optical waveguides. Sidewall growth is eliminated by the presence of a dielectric spacer layer which covers the sidewalls. We demonstrate the effectiveness of this process by selective-area growth of Ge and Ge/SiGe quantum wells, and show an improved performance and increased process reliability over previous work.

©2012 Optical Society of America

**OCIS codes:** (220.0220) Optical design and fabrication; (250.4110) Modulators; (200.4650) Optical interconnects; (130.3130) Integrated optics materials; (230.7370) Waveguides.

### References and links

- J. Michel, J. Liu, and L. C. Kimerling, "High-performance Ge-on-Si photodetectors," Nat. Photonics 4(8), 527– 534 (2010).

- M. Kim, O. O. Olubuyide, J. U. Yoon, and J. L. Hoyt, "Selective epitaxial growth of Ge-on-Si for photodiode applications," ECS Trans. 16, 837–847 (2008).

- S. Ren, Y. Rong, S. A. Claussen, R. K. Schaevitz, T. I. Kamins, J. S. Harris, and D. A. B. Miller, "Ge/SiGe quantum well waveguide modulator monolithically integrated with SOI waveguides," IEEE Photon. Technol. Lett. 24(6), 461–463 (2012).

- N. N. Feng, S. Liao, D. Feng, X. Wang, P. Dong, H. Liang, C. C. Kung, W. Qian, Y. Liu, J. Fong, R. Shafiiha, Y. Luo, J. Cunningham, A. V. Krishnamoorthy, and M. Asghari, "Design and fabrication of 3µm silicon-on-insulator waveguide integrated Ge electro-absorption modulator," Opt. Express 19(9), 8715–8720 (2011).

- H. Ishii, Y. Takahashi, and J. Murota, "Selective Ge deposition on Si using thermal decomposition of GeH<sub>4</sub>," Appl. Phys. Lett. 47(8), 863–865 (1985).

- S. Ren, Y. Rong, T. I. Kamins, J. S. Harris, and D. A. B. Miller, "Selective epitaxial growth of Ge/Si<sub>0.15</sub>Ge<sub>0.85</sub> quantum wells on Si substrate using reduced pressure chemical vapor deposition," Appl. Phys. Lett. 98(15), 151108 (2011).

- 7. W. Franz, "Influence of an electric field on an optical absorption edge," Z. Naturforsch. B 13a, 484-489 (1958).

- L. V. Keldysh, "The effect of a strong electric field on the optical properties of insulating crystals," Sov. Phys. JETP 7, 788–790 (1958).

- Y. H. Kuo, Y. K. Lee, Y. Ge, S. Ren, J. E. Roth, T. I. Kamins, D. A. B. Miller, and J. S. Harris, "Strong quantum-confined Stark effect in germanium quantum-well structures on silicon," Nature 437(7063), 1334–1336 (2005)

- D. A. B. Miller, "Device requirements for optical interconnects to silicon chips," Proc. IEEE 97(7), 1166–1185 (2009).

- 11. G. T. Reed, G. Mashanovich, F. Y. Gardes, and D. J. Thomson, "Silicon optical modulators," Nat. Photonics 4(8), 518–526 (2010).

- N. N. Feng, P. Dong, D. Zheng, S. Liao, H. Liang, R. Shafiiha, D. Feng, G. Li, J. E. Cunningham, A. V. Krishnamoorthy, and M. Asghari, "Vertical p-i-n germanium photodetector with high external responsivity integrated with large core Si waveguides," Opt. Express 18(1), 96–101 (2010).

- S. Ren, T. I. Kamins, and D. A. B. Miller, "Thin dielectric spacer for the monolithic integration of bulk germanium or germanium quantum wells with silicon-on-insulator waveguides," IEEE Photon. J. 3(4), 739–747 (2011).

- A. Nayfeh, C. O. Chui, K. C. Saraswat, and T. Yonehara, "Effects of hydrogen annealing on heteroepitaxial-Ge layers on Si: Surface roughness and electrical quality," Appl. Phys. Lett. 85(14), 2815–2817 (2004).

### 1. Introduction

The ability to selectively grow germanium in specific regions of a silicon substrate is highly desirable for the future integration of Ge-based optoelectronice devices with high-speed Sibased electronic circuits. Potential applications include dense integration of high-performance photodetectors [1,2] and optical modulators [3,4]. While selective-area growth of Ge has been investigated since the mid-1980s [5], using these growth processes in the fabrication of actual devices often introduces additional challenges. For example, selective growth of Ge is commonly carried out by using a dielectric mask such as silicon dioxide (SiO<sub>2</sub>) or silicon nitride (Si<sub>3</sub>N<sub>4</sub>) above the Si substrate. Growth windows are etched through the dielectric and Ge growth is initiated at the exposed Si surface [1,6]. Certain device designs [3,4] require growth of a Ge region inside a Si optical waveguide, with the growth regions etched through the dielectric layer and into the underlying Si waveguide layer. Since any exposed crystalline silicon surface can serve as a growth template for the Ge, the exposed Si sidewalls initiate deleterious growth that affects both the optical and electronic properties of the device. In this work, we propose and demonstrate a fabrication process to reliably prevent growth on these Si sidewalls, even in relatively thick structures, and demonstrate highly selective growth of both Ge and SiGe.

Ge and Ge/SiGe quantum wells (OWs) both exhibit electroabsorption effects (the Franz-Keldysh effect in bulk Ge [7,8] and the quantum confined Stark effect (OCSE) in Ge/SiGe QWs [9]), where an increase in the applied electric field redshifts the absorption spectrum of the material. This behavior allows the development of compact, high-performance, Ge-based Si-compatible optical modulators for optical interconnect applications [10,11]. Waveguidebased modulators allow for longer interaction lengths between the optical beam and the active material and easier integration with other on-chip optical components. However, to minimize loss from background absorption in Ge structures, the modulator region must be integrated with low-loss entrance and exit waveguides, such as silicon-on-insulator (SOI) waveguides. These waveguides can be single-mode while still being relatively thick. Coupling between the active Ge region and the passive waveguide can be carried out either evanescently using adiabatic tapers [12] or through direct butt coupling [3]. In the case of adiabatic coupling, a Ge layer is grown directly above the Si layer of the SOI substrate. The adiabatic tapers used are typically very long, increasing the footprint of the device and, if formed out of the active Ge material, increasing the device capacitance. Growing the Ge or Ge/SiGe QWs in growth windows directly in the SOI waveguide, butt-coupling the modulation region to the input and output waveguides, enables a modulator with a small footprint and low capacitance. However, these growth windows can have very thick sidewalls of exposed Si (depending on the thickness of the SOI waveguide), where Ge growth is expected to occur if preventative steps are not taken.

This growth on the exposed Si sidewalls needs to be avoided because it can significantly disturb the planarity of the device, making post-growth fabrication and integration with other devices difficult or requiring chemical mechanical polishing (CMP). Planarity is also important for the optimal performance of heterostructures like QWs. Furthermore, for active devices that rely on *pn* or *p-i-n* junctions that are doped *in situ* during growth, growth on the sidewalls can lead to electrical shorting of the device or high leakage current.

## 2. Design motivation

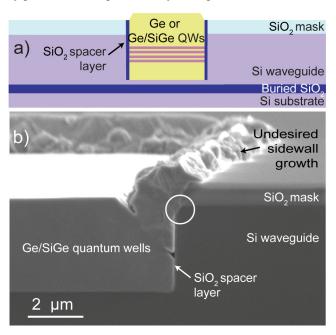

To prevent sidewall growth and enable high-quality growth in the desired regions, a process was previously proposed to deposit a dielectric spacer on the sidewalls of the growth windows [13]. Figure 1(a) shows a schematic of the designed substrate, with Ge/SiGe QW growth in the growth window of an SOI waveguide. (It should be noted that while much of the discussion here focuses on integration with 3 µm-thick SOI waveguides because this is the desired application, the results transfer completely to applications that require selectively growing in growth windows etched into bulk Si substrates or SOI waveguides of different thicknesses. In fact, much of the development of this work and the results shown here were

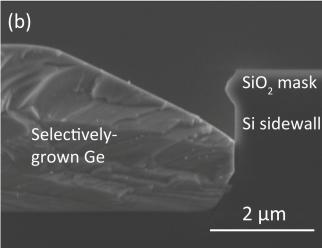

done using Si substrates.) Unfortunately, while this previously proposed spacer fabrication process did allow the demonstration of high-quality QW growth, it was not robust to minor fabrication variations, making mode-matched growth with SOI waveguides unreliable. Figure 1(b) presents a typical result, with excessive sidewall growth visible and planar QW growth at the center of the growth window. Despite many efforts to modify this fabrication process, it proved to be very sensitive to minor process variations, which led to poor repeatability and yield. A weak point in the approach was determined to be at the top corner of the Si sidewall, directly under the SiO<sub>2</sub> growth mask. The dielectric spacer was likely removed from this corner during a dry etching step in the substrate fabrication, if the spacer layer at this corner was not sufficiently protected during the etch by the top SiO<sub>2</sub> mask.

Fig. 1. (a) Desired growth results using the substrate preparation process suggested by Ren *et al.* [13]. (b) Scanning electron microscope (SEM) image of selective area growth of Ge/SiGe QWs. Implementation of the spacer fabrication process proved to be not very robust, and often resulted in undesired sidewall growth originating from the top corner of the Si sidewall, directly under the SiO<sub>2</sub> mask edge (circled region). The dielectric spacer was likely removed from this corner during a dry etching step in the substrate fabrication, due to insufficient coverage of the spacer by the top SiO<sub>2</sub> mask.

To overcome this problem of unreliable spacer fabrication and thus substantial sidewall growth, we propose a change in the original spacer fabrication process set forth by Ren *et al.* [13] that renders it independent of process variations. When determining a potential fabrication process for the spacer, a few considerations need to be kept in mind. First, it is desirable to make the spacer as thin as possible, to minimize optical loss [13]. The spacer needs to also be formed only on the vertical sidewalls of the growth window, not at the bottom of the window, where the epitaxial growth is initiated. Finally, great care needs to be taken so that the spacer fabrication does not damage this growth surface at the bottom of the window.

# 3. Fabrication process

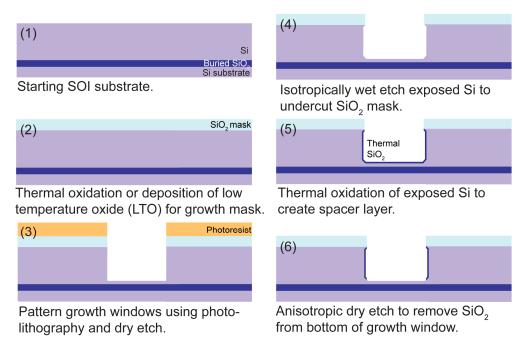

Figure 2 illustrates the new proposed process. Beginning with either a Si or SOI wafer, the SiO<sub>2</sub> growth mask is formed through thermal oxidation or through deposition of low-temperature oxide (LTO) via low-pressure chemical vapor deposition (LPCVD). If this latter option is used, the LTO is densified at 1100°C for 1 hour to reduce the number of dangling

bonds present; any such dangling bonds likely contribute to undesired growth nucleation on the top  $SiO_2$  surface. We found that using thermal  $SiO_2$  or densified LTO as the growth mask give comparable selectivity results under the growth conditions used here. Then, the growth windows are patterned using standard photolithography. The top  $SiO_2$  layer is etched using a CHF<sub>3</sub>/O<sub>2</sub> reactive ion etch (RIE). Then, the Si is etched using a timed HBr/Cl<sub>2</sub>/O<sub>2</sub> RIE etch to the desired depth. Because this process was designed for use on an SOI substrate with a 3 µmthick Si device layer, the growth windows were etched ~2.8 µm into the Si, to allow a sufficiently thick remaining Si layer (~200 nm) to initiate epitaxial growth. The process up to this point (Step 3 in Fig. 2) is identical to that adopted in the previous process shown in Fig. 1.

Fig. 2. Proposed new dielectric spacer fabrication process. The  $SiO_2$  spacer on the sidewalls is protected by the overhanging  $SiO_2$  mask layer, preserving it during subsequent fabrication steps and ensuring that the sidewall remains completely covered.

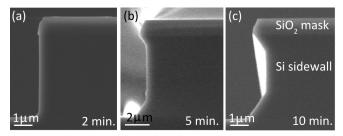

In our new process, however, following removal of the photoresist, the Si device layer is etched in a wet etchant to undercut the Si sidewalls. Room temperature tetramethylammonium hydroxide (TMAH) was used here. As shown in Fig. 3, the undercut can be controlled by the etch time used. Following this wet etch, the wafer is thermally oxidized to form the SiO<sub>2</sub> spacer layer. The simulations by Ren *et al.* show that optical reflections and scattering off this spacer layer decrease as the thickness of the SiO<sub>2</sub> layer decreases [13]. Thus, the spacer should only be as thick as is necessary for full coverage of the sidewall. In this work, we targeted a final spacer thickness of 80 nm, which Ren *et al.* predict will transmit about 80% of the optical power [13]. This thermal oxidation step also serves to remove damage to the Si surface at the bottom of the growth window that may have occurred during dry etching of this region.

Fig. 3. Longer wet etch times of the Si sidewalls lead to greater amounts of undercut, as shown by these cross section SEM images of samples that were etched for (a) 2 minutes, (b) 5 minutes, and (c) 10 minutes. The wet etch used in this work, tetramethylammonium hydroxide, etches different crystal planes of Si at different rates, resulting in the faceting evident at longer etch times

Finally, an anisotropic dry etch followed by a very short wet etch in 20:1 buffered oxide etch (BOE) are used to remove the thermal SiO<sub>2</sub> from the bottom of the growth window while leaving it on the sidewalls. The key to the success of this process is the presence of the overhanging SiO<sub>2</sub> growth mask, which serves to protect the spacer on the sidewalls from being etched while the SiO<sub>2</sub> layer at the bottom of the growth window is dry etched. During the subsequent selective buffered oxide wet etch, the thickness of the SiO<sub>2</sub> at the bottom of the growth window is much less than that on the sidewalls. Thus, the bottom of the growth window can be completely cleared of SiO<sub>2</sub> while a continuous layer is maintained on the sidewalls, including at the top edge of the Si sidewall directly under the SiO<sub>2</sub> growth mask layer, which was a weak point in the previous process design of Fig. 1.

### 4. Epitaxial growth conditions

In this work, both Ge/SiGe quantum well samples and pure Ge samples were epitaxially grown on either a Si(001) substrate or a silicon-on-insulator substrate (with a 3  $\mu$ m Si device layer and 375 nm buried oxide layer) in an Applied Materials Centura reduced-pressure chemical vapor deposition (RPCVD) reactor. The growth process used GeH<sub>4</sub> and SiH<sub>4</sub> in a H<sub>2</sub> carrier gas at a temperature of 405°C and a system pressure of 40 Torr. No HCl was added to the process gases so selectivity was not optimal. To decrease the defect density and surface roughness, the quantum wells were grown on p-type Si<sub>0.12</sub>Ge<sub>0.88</sub> buffer layers (*in situ* doped with boron) that underwent high temperature hydrogen annealing; the pure Ge samples also undergo multiple hydrogen anneals for heteroepitaxy (MHAH) [9,14]. To prevent dopant diffusion into the quantum wells, a layer of intrinsic Si<sub>0.12</sub>Ge<sub>0.88</sub> was grown both before and after the quantum well region. The absorbing region consisted of 20 quantum wells which were 15 nm wide with 35 nm barriers and a top capping layer of *n*-type, arsine-doped Si<sub>0.12</sub>Ge<sub>0.88</sub>.

# 5. Results and conclusion

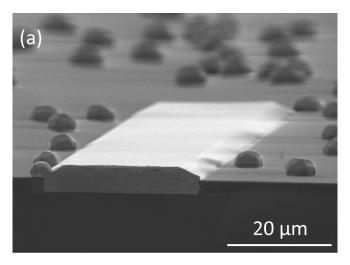

As shown in Fig. 4, this altered design reliably leads to high-quality Ge growth with minimal sidewall growth. For this result, a 5 minute TMAH wet etch was used, to ensure an adequate undercut of the Si sidewall while not greatly distorting the profile of the interface between the Si waveguide and the Ge modulation region.

Crystal faceting at the sidewalls, which has been observed in other selective-area growth work [1,6], is evident and points to well-controlled and high-quality growth. This faceting is believed to be due to different crystal planes of Ge or SiGe growing at different rates, depending on the growth temperature used [6]. Furthermore, the process developed here is simpler than the previously proposed one, with fewer process steps. This fact, combined with the robustness that is built into the process design due to the presence of the overhanging  $SiO_2$  masking layer, leads to much higher yields.

Fig. 4. SEM images of selective-area Ge growth using the dielectric spacer fabrication process in Fig. 2. (a) Angled image of a sample etched in TMAH for 5 minutes. Ge nucleation is evident on the top surface of the  $SiO_2$  mask, indicating imperfect selectivity. (b) Cross section SEM showing Ge crystal facets at the edge of the growth window.

Random nucleation of the Ge growth occasionally occurred on the oxide-covered sidewalls and the top oxide growth mask, as seen in Fig. 4. (This nucleation was also present when the previous substrate fabrication process was employed, though it cannot be observed in Fig. 1 due to the smaller SEM window of that image.) The density of growth nucleation varies, as the area of these clusters increases with increasing growth times. With the thick 2-5 μm growths used in this work, the nucleation would typically cover less than 10% of the surface area of the top oxide growth mask. We expect such nucleation could occur especially at broken bonds on the oxide surface. Thermally grown oxide or adequately annealed deposited oxide are expected to have a low density of broken bonds on the surface; this is the reason we perform a high temperature anneal following the initial deposition of the LTO growth mask. Great care is taken to repair any possible damage to this top oxide layer that may be incurred during the subsequent spacer fabrication process. Specifically, exposure to a plasma during dry etching can break bonds and provide growth nucleation sites. Thus, following the final dry etch step (Fig. 2 Step 6), a high temperature anneal is performed on the substrates (1050°C for 1 hour) to try to repair this dry etch damage to the oxide growth mask. However, as shown in Fig. 4, it was difficult to completely prevent this nucleation from

occurring; this would require extensive development of new growth recipes, for example using HCl to inhibit nucleation, which was not carried out in this work.

In conclusion, we have developed and demonstrated a process for preparing substrates for selective-area epitaxial growth of Ge and Ge/SiGe QWs in growth windows etched into the Si substrate or Si waveguides. This fabrication process results in a thin dielectric layer completely covering the exposed Si sidewalls of the growth region, preventing Ge growth from occurring on the sidewalls and restricting it to only the bottom of the growth window, as desired. This process enables future integrated low-loss, high-performance Ge and Ge/SiGe QW waveguide modulators and photodetectors monolithically integrated with SOI waveguides.

# Acknowledgments

This work was supported in part by Oracle under contract HR0011-08-9-0001 between the Government and Oracle. The views, opinions, and/or findings contained in this article are those of the authors and should not be interpreted as representing the official views or policies, either expressed or implied, of the Defense Advanced Research Projects Agency or the Department of Defense. The authors also acknowledge the support of the IFC Focus Center, one of six research centers funded under the Focus Center Research Program, a Semiconductor Research Corporation program. K.C. Balram and E.T. Fei acknowledge the support of a Stanford Graduate Fellowship. Work was performed in part at the Stanford Nanofabrication Facility (a member of the National Nanotechnology Infrastructure Network) which is supported by the National Science Foundation under Grant ECS-9731293, its lab members, and the industrial members of the Stanford Center for Integrated Systems.