# Electronics for Ultrasonic Imaging System

L. Svilainis<sup>1</sup>, V.Dumbrava<sup>1</sup>, S. Kitov<sup>1</sup>, A. Aleksandrovas<sup>1</sup>, P. Tervydis<sup>1</sup>, D. Liaukonis<sup>1</sup> Department of Electronics Engineering, Kaunas University of Technology, Studentu St. 50–340, LT-51368 Kaunas, Lithuania linas.svilainis@ktu.lt

Abstract—Design of ultrasonic imaging system is presented. System has a modular structure with main acquisition and front end electronics separated in order to have minimal path for host PC connectivity and shortest path to ultrasonic transducer. Such acquisition modules placement allows reducing the induced EMI and increasing the flexibility of the system. Positioning module is also separate and allows various scanning equipment configurations. Evaluation of excitation and reception electronics parameters is presented. Essential measurement procedures outlined. Signal digitization parameters (sampling frequency, clock jitter and quantisation) were chosen to balance time of flight estimation random errors versus interpolation bias errors.

Index Terms—Ultrasonic imaging, ultrasound electronics, data acquisition, signal sampling.

#### I. INTRODUCTION

Thanks to the direct interaction with material structure ultrasonic probing can extract the mechanical properties related information which later can be used in measurement or imaging. Ultrasonic imaging is used in non-destructive testing (NDT) and evaluation (NDE) [1]-[3]. Coating or layers thickness can be measured [4], mechanical properties evaluation [5], non-contact temperature visualization [6], surface profiling [7], medical diagnostic, tissue temperature or elasticity imaging [8]. Ultrasonic system can be small [9], [10] equipment is safe and easy in exploitation. Quality of the image obtained is defined by the imaging method used, ultrasonic transducer and signal acquisition electronics. If system is dedicated for particular task, then it is important to keep the size and the price of the electronics down. In such case functionality and data quality are sacrificed. System flexibility and acquisition quality is essential in ultrasonic data acquisition for research purposes.

The goal of this paper is to present the design and development of the electronics of the ultrasonic imaging system. Ultrasonic data acquisition system has to carry several tasks: provide the excitation signal for ultrasonic transducer; position the transducer; receive and process the received signal; transfer data to or from PC. Modular construction was suggested in order to ensure the flexibility of the system. Parameters of the main units were selected to match the expected performance and balanced in a sense of power consumption, size and price. Design considerations and parameters evaluation procedures are presented.

Manuscript received January 27, 2014; accepted April 14, 2014.

This research was funded by a project IN-SMART, grant No. VP1-3.1-SMM-10-V-02-012

#### II. SYSTEM STRUCTURE

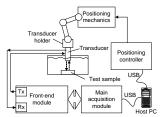

Data acquisition system for ultrasonic imaging has been designed (Fig. 1). System is modular: i) front-end module; ii) main acquisition module; and iii) positioning module.

Fig. 1. General system structure showing its modular construction.

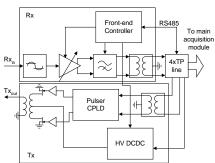

Front-end module (Fig. 2) is placed in close proximity to ultrasonic transducer in order to reduce the electromagnetic interference. This module contains high voltage pulser (Tx), programmable high voltage power source and low noise preamplifier with high voltage protection circuits (Rx).

Fig. 2. Analog front-end module structure.

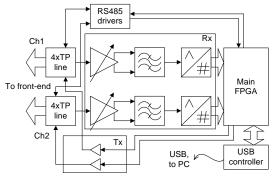

Main acquisition module (Fig. 3) is located near the host PC. It contains the excitation signal transmission unit (Tx) and the signal reception unit (Rx). Transmission unit contains buffer drivers which route the driving signals to excitation part of the front-end module. Driving signals are derived from RAM organised in main FPGA. Reception unit is responsible for additional gain of the incoming signal, analog filtering, analog-to-digit conversion (ADC), digital signal processing and data transfer (Rx). FPGA is used for ADC data storage management, serial communication with front-end module, communication with GPIO part of the USB controller and synchronisation.

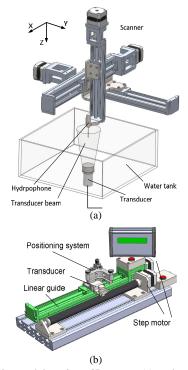

Positioning module contains the controller, motor drivers and positioning mechanics. Controller is capable of steering of up to four motor controllers. Several options of the positioning mechanics can be used: i) universal 3D positioning scanner or ii) dedicated translation stage (Fig. 4).

Fig. 3. Main acquisition module structure.

Fig. 4. Positioning module options: 3D scanner (a) or sleeve (b).

All modules are replaceable in order to attain different functionality. E.g. analog front-end can be replaced by multichannel module, allowing phased array imaging or fast electronic scan.

Design considerations and parameter measurements of the aforementioned units are presented below.

## III. EXCITATION ELECTRONICS

As can be seen from Fig.1 the ultrasonic transducer is main device connecting the electrical and acoustical parts of the system. It is used to convert the electrical power into mechanical energy and vice versa [11]. Mechanical stress propagating in the test material is interacting with material structure in the propagation path and in case of mechanical impedance mismatch is reflected back. Flaws in the material can be located by analysing the reflected signals. The most common transducer types represent the capacitive load to the excitation electronics. Therefore main task of the excitation circuit is a fast charge and discharge of the capacitive load. Most common type excitation signal is a rectangular pulse or step [12], [13].

Usually power MOSFET is used as a power switch thanks to its speed and high current delivery capability [13], [14].

In order to remove the charge from  $C_0$  at the end of excitation pulse additional element is needed to pull the output voltage low. Conventional pulser topology where only one active element and return resistor are used [13] is not suitable here - return resistor draws current during the excitation pulse lowering the overall system efficiency. The most attractive is the totem pole topology [14]–[16]. This topology is using two N-channel MOSFETs. Full voltage swing can be applied here. Problem with such configuration is the delivery of the driving signal to high side switch: floating driver and power supply are needed here. Therefore topology is mainly used for voltage below 100 V [15] or high voltage but low frequency [14]. Using P-channel MOSFET for high side driving is more convenient [16] but performance still suffers since high voltage P-channel MOSFETs are slow.

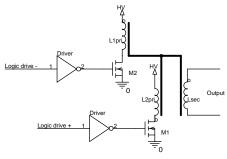

Another possible topology is the transformer push-pull [17], [18] (Fig. 5). Low side switches can be used here. Summation is accomplished using the transformer.

Fig. 5. Pulser output topology: transformer push-pull with two MOSFETs.

Main advantage is the ability to use low side drivers; symmetrical driving conditions for both rising and falling edges; output isolation and possibility to have positive and negative pulses using only one high voltage power supply. Fast switching is possible thanks to optimal driving circuit topography.

## A. Pulser Output AC Response Estimation

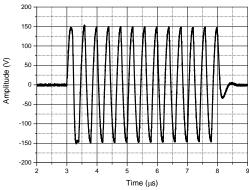

Output signals were registered by the same acquisition system (Fig. 1). Excitation signal was preloaded into system memory as ten periods long CW burst (Fig. 6).

Fig. 6. Pulser output waveform example when used for AC response.

Main harmonic amplitude was extracted using the Sine Wave Correlation (SWC) technique. SWC technique [19] can be treated as partial Fourier transform. Correlation coefficient of the signal sampled version  $s_n$  with sine and

cosine functions:

$$\begin{cases} C(f) = \frac{2\sum_{n=0}^{N-1} \left[\cos\left(2f \ ft_n\right) \times s_n \times w_n\right]}{N|W|_1}, \\ S(f) = \frac{2\sum_{n=0}^{N-1} \left[\sin\left(2f \ ft_n\right) \times s_n \times w_n\right]}{N|W|_1}, \end{cases}$$

(1)

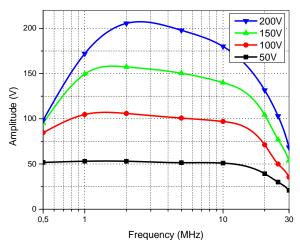

where  $w_n$  is a window function, N is record length and  $|W|_1$  is a L1 norm of the window function. For output response measurements rectangular window was used: recorded signal was cropped to exactly ten periods of the fundamental frequency. Pulser output signals were recorded using 1:100 divider formed by 5 k $\Omega$  and 50  $\Omega$  resistors which was also accounted in calculations. Resulting output AC response is presented in Fig. 7.

Fig. 7. Pulser output AC response versus voltage swing ±.

It can be seen that excitation up to 25 MHz is achieved. Available bandwidth is reduced with increase of the excitation voltage span.

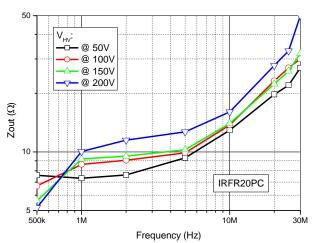

### B. Pulser Output Impedance Measurement

Interaction of the pulser output impedance and transducer input impedance will cause the variation of the excitation voltage. In order to keep this voltage constant and be able to predict the efficiency of power delivery to transducer [14] investigation of pulser output impedance  $Z_0$  was carried out.

Pulser output impedance  $Z_0$  together with the impedance  $Z_T$  of the ultrasonic transducer can be used for power delivery efficiency evaluation [14]. It can be assumed that real part of complex power delivered to ultrasonic transducer reflects the power transmitted by transducer (if transducer design is optimal). Then the power delivery to ultrasonic transducer efficiency is

$$y = \frac{4 \operatorname{Re}(Z_o) \operatorname{Re}(Z_T)}{|Z_o + Z_T|^2} 100\%,$$

(2)

Pulser output impedance was measured by taking two output voltages registered at 50  $\Omega$  ( $V_{50}$ ) and 75  $\Omega$  ( $V_{75}$ ) load conditions [19], [20]

$$Z_o = \frac{50 \times 75 \times (V_{75} - V_{50})}{75 \times V_{50} - 50 \times V_{75} N_0},\tag{3}$$

Fig. 8. Pulser output impedance versus frequency.

Complex voltage values were obtained by using the SWC. Results for output impedance magnitude AC response versus output voltage swing are presented in Fig. 8. It can be noted that output impedance magnitude is stable with output voltage and is rising with output frequency (5  $\Omega$  to 30  $\Omega$ ).

## C. Pulser Power Consumption Evaluation

Pulser is using two switches to save the energy when there are no level transitions. In such case energy is consumed only during the level transitions due to cross-conduction losses and due to the parasitic capacitance at the MOSFET output. Efficiency of pulser was evaluated using the energy consumption per pulse criteria for several load conditions. It was calculated using the high voltage supply power consumed  $P_{\rm HV}$ , burst repetition frequency PRF, number of pulses N in a burst

$$E_{pp} = \frac{P_{HV}}{PRF \times N}.$$

(4)

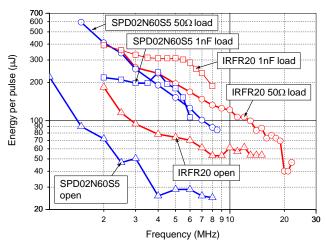

Energy per pulse energy consumption for 200 V output at 1 nF,  $50\,\Omega$  load and unloaded condition for two MOSFET types is presented in Fig. 9.

Fig. 9. Energy per pulse consumption under several load conditions.

It can be seen that higher drain peak current of IRFR20

(8 A vs. 3 A) allows higher operation frequency. Yet reduced peak current of the SPD02N60S5 gives tenfold reduction in power losses.

# IV. RECEIVING ELECTRONICS

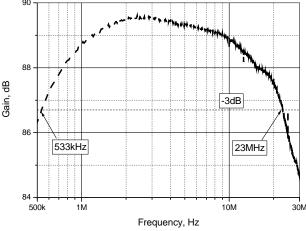

Low noise variable gain amplifier AD8031 was used in reception channel. Receiving electronics define the reception performance of the whole system. Total system gain is 80 dB with operation bandwidth 0.5 MHz to 25 MHz.

# A. System AC Response

System AC response (Fig. 10) was obtained using same SWC technique. Input was fed by harmonic signal from direct digital synthesizer, driven by the clock source derived from the ADC channel. Signal at the input  $u_{\rm in}$  was registered by ADC1 (Fig. 3) and the output signal  $u_{\rm out}$  was connected to channel ADC2. Taking the ratio of two complex voltages the complex amplifier gain was obtained. Output AC response  $u_{\rm out}$  was divided by input AC response  $u_{\rm in}$

$$G(f) = \frac{u_{out}(f)}{u_{in}(f)}.$$

(5)

For this type of measurements Hamming window was used instead of rectangular window: it was complicated to match exact number of periods of the fundamental frequency into analysis window. It can be seen that operation range is slightly reduced at maximum gain.

Fig. 10. System AC response at maximum gain setting.

Preamplifier parameters are essential for reception performance so it was investigated separately.

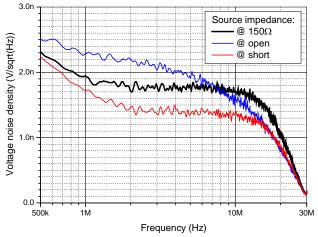

## B. Receiver Noise Evaluation

System output was sampled by ADC in order to investigate reception channel noise. Record of 32 k samples was taken thousand times with passive component connected at the system input (open, 150  $\Omega$  resistor, and shorted or 0  $\Omega$  resistor). Fourier transform has been used to obtain the noise power spectral density

$$nPSD_{k} = \frac{2\sum_{c=1}^{C_{\text{max}}} \left| \sum_{n=0}^{N-1} s_{n} e^{-i\frac{2f}{N}nk} \right|^{2}}{f_{s}C_{\text{max}}NG_{sys}} = \frac{nPSD_{ADC}}{G_{sys}}.$$

(6)

Fig. 11. Input-referred noise voltage density of the system.

Obtained noise power spectral density nPSD was powerwise averaged, divided by gain AC response (Fig. 10) and square root taken to obtain the statistical voltage noise density estimate at the system input (Fig. 11).

Noise measurements confirm that input voltage noise in case of 150  $\Omega$  signal source is 2 nV/ $\sqrt{Hz}$ .

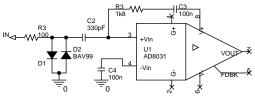

# C. Preamplifier Input Impedance

Preamplifier input impedance was designed for  $1 \text{ k}\Omega$  using active impedance matching (R3, Fig. 12).

Fig. 12. Preamplifier input circuit topology with active input matching.

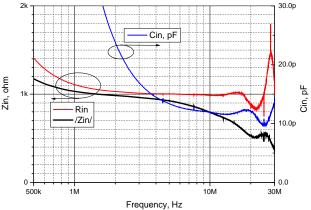

Parasitic capacitances of the layout and ICs will distort the situation. In order to confirm that design has reached targeted input impedance, preamplifier input impedance measurements were carried out using the technique described in [19] (Fig. 13).

Fig. 13. Preamplifier input impedance AC response.

It can be seen that input impedance is  $1\,\mathrm{k}\Omega$  and stable within passband. Parasitic input capacitance slightly reduces input impedance magnitude at frequencies beyond 10 MHz.

## D. Preamplifier Input Protection

Preamplifier input is exposed to high voltage pulses [21].

Hard diode limiter input protection was used (Fig. 14).

Fig. 14. Preamplifier recovery time measurement circuit.

Recovery time of the ultrasonic preamplifier is important if signal's acquisition is carried out in close vicinity of the transducer face [22].

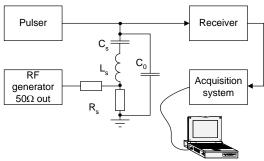

Recovery time was estimated using technique described in [23]: i) preamplifier input was fed with sinusoidal signal via electrical model of the ultrasonic transducer, ii) system output response (Fig. 15) was registered while driving the input by rectangular high voltage pulse.

Fig. 15. Explanatory time diagrams of the recovery time measurement.

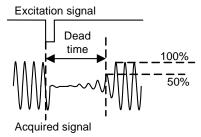

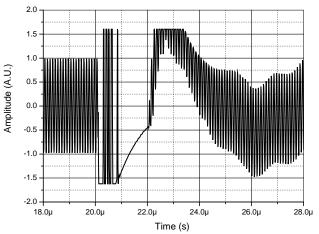

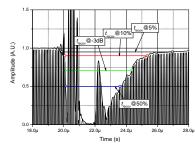

When excitation signal appears at the receiver input then preamplifier circuit is saturated and no CW signal is present at the receiver output. After excitation pulse is removed, circuit starts to recover from saturation and CW signal amplitude starts growing (Fig. 16).

Fig. 16. Signal at the system output during the excitation pulse.

Dead time was estimated by noting the time instant when signal level is crossing the predetermined threshold level. Recorded signal was filtered to remove low frequency components. Bandpass (BP) filter equal to 100 % of the transducer bandwidth was used to extract the component of the fundamental frequency. Hilbert transform was used to obtain the envelope

$$\left| s_k \right| = \left| IDFT \left( 2 \times \left( DFT \left( s_k \right) \right), \check{S} \ge 0 \right) \right|, \tag{7}$$

where DFT and IDFT are discrete forward and inverse Fourier transform respectively, as defined in (3).

Envelope was used for recovery time estimation at -5 %–10 %, -3 dB and -50 % convergence threshold (Fig. 17).

Fig. 17. Signal used for preamplifier recovery time estimation.

Recovery time was estimated as  $2.5 \,\mu s$  at  $-5 \,\%$  level  $2.3 \,\mu s$  at  $-10 \,\%$  level and  $2.1 \,\mu s$  at  $-3 \,dB$  level.

## V. SIGNAL DIGITIZATION ELECTRONICS

The ability to process the ultrasonic signal digitally is offering multiple advantages. Transformation of the signal into digital domain alters signal content. Noise component at reception channel output  $e_{\text{ntotAout}}$  (ADC input) has to be augmented to account the quantization noise  $e_{\text{nQ}}$  and reference clock jitter noise  $e_{\text{nJ}}$  [24]

$$e_{ntot}^2 = e_{ntotAout}^2 + e_{nQ}^2 + e_{nJ}^2.$$

(8)

In [24] it was shown that if expected electronics noise at reception channel output  $e_{\text{ntotAout}}$  is  $180 \text{ nV/}\sqrt{\text{Hz}}$  (output noise of AD8031 at minimum gain) then no more than 20 ps jitter clock is required to avoid the clock jitter noise influence. In order to make the quantization noise influence insignificant the resolution of ADC has to be above 9 bits at 100 MHz sampling frequency.

Time of flight (ToF) estimation variance was used as optimization criteria in further analysis. Subsample interpolation case was considered. It was shown [25] that interpolation bias error exists in ToF subsample estimation if truncated interpolation function is used. For cosine [25] interpolation this error is

$$\max\left[V(ToF_c)\right] = \sqrt{f} \frac{s^2}{f_s^3}.$$

(9)

And for parabolic interpolation it is

$$\max\left[V(ToF_p)\right] = \max\left[V(ToF_c)\right] + \frac{f_0^2}{\sqrt{2f_s^3}}.$$

(10)

From (9) and (10) it follows that interpolation errors are influenced by signal parameters (envelope bandwidth S and center frequency  $f_0$ ) and sampling frequency.

ToF estimation random errors that are caused by noise can

be estimated using Cramer-Rao lower error bound

$$\uparrow (TOF) \ge \frac{1}{2f F_e \sqrt{SNR}},\tag{11}$$

where  $SNR = \frac{2E}{N_0}$ , E is signal energy,  $F_e$  is effective

bandwidth of the signal and  $N_0$  is the noise power density. With signal and noise measurements available, equations (9) (10) and (11) can be reversed to derive the minimum sampling frequency. In case of cosine interpolation it is

$$f_{s\_\min\_\cos} \ge \sqrt[3]{\sqrt{18f^3} \times S^2 F_e \sqrt{SNR}}.$$

(12)

In [25] it was shown that if signal-to-noise ratio is highest possible (180 nV/ $\sqrt{\text{Hz}}$  output noise of the reception channel) then minimum sampling frequency should be 67 MHz for pulse and 101 MHz for wideband chirp. Combining all the analysis 100 MHz 10 bit ADC AD9214BRSZ-105 was chosen with clock oscillator ASEMPC (3 ps jitter). Such acquisition configuration ensures that digitization errors are kept below random errors defined by analog components and 9 ps ToF uncertainty can be achieved in measurements.

## VI. CONCLUSIONS

Design of ultrasonic imaging system electronics was presented. System allows exciting and collecting signals in (0.5 ... 25) MHz range. Excitation signal voltage can reach  $\pm 200$  V. Input impedance was designed 1 k $\Omega$  using active impedance matching. Input impedance was confirmed by measurements. System input noise is low: measurements indicate that input voltage noise density in case of 150  $\Omega$  signal source is 2 nV/\delta Hz. Recovery time was estimated as 2.1  $\mu s$  at -3 dB threshold level. Modular design offers configuration flexibility: both single and multichannel configurations are available. Acquisition parameters are optimized.

#### REFERENCES

- [1] A. M. T. Hassan, S. W. Jones, "Non-destructive testing of ultrahigh performance fibre reinforced concrete (UHPFRC): A feasibility study for using ultrasonic and resonant frequency testing techniques", Construction and Building Materials, vol. 35, pp. 361–367, 2012. [Online]. Available: http://dx.doi.org/10.1016/j.conbuildmat. 2012.04.047

- [2] A. J. Hunter, et al., "Autofocusing ultrasonic imagery for non-destructive testing and Evaluation of specimens with complicated geometries", NDT&E International, vol. 43, pp. 78–85, 2010. [Online]. Available: http://dx.doi.org/10.1016/j.ndteint.2009.09.001

- [3] S. K. Nath, et al., "An Ultrasonic Time of Flight Diffraction Technique for Characterization of Surface-Breaking Inclined Cracks", Materials Evaluation, vol. 67, no. 2, pp. 141–148, 2009.

- [4] R. Raisutis, R. Kazys, L. Mazeika, "Ultrasonic Thickness Measurement of Multilayered Aluminum Foam Precursor Material", *IEEE Trans. Instrum. Meas*, vol. 57, no. 12, pp. 2846–2855, 2008. [Online]. Available: http://dx.doi.org/10.1109/TIM.2008.927208

- [5] T. Chudoba, M. Griepentrog, A. Duck, D. Schneider, F. Richter, "Young's modulus measurements on ultra-thin coatings", *Journal of Materials Research*, vol. 19, no 1, pp. 301–314, 2004. [Online].

- Available: http://dx.doi.org/10.1557/jmr.2004.19.1.301

- [6] T. H. Gan, D. A. Hutchins, "Air-coupled ultrasonic tomographic imaging of high-temperature flames", *IEEE Trans. Ultrason.*, *Ferroelect., Freq. Control*, vol. 50, no. 9, pp. 1214–1218, 2003. [Online]. Available: http://dx.doi.org/10.1109/TUFFC.2003.1235334

- [7] D. Roth, H. Kautz, P. Abel, "Three dimensional surface depression profiling using focused air coupled ultrasonic pulses", *Materials evaluation*, vol. 59, no. 4, pp. 543–548, 2001.

- [8] M. Tanter, D. Touboul, J. L. Gennisson, J. Bercoff, M. Fink, "High-Resolution Quantitative Imaging of Cornea Elasticity Using Supersonic Shear Imaging", *IEEE Trans. Medical Imaging*, vol. 28, no. 12, pp. 1881–1893, 2009. [Online]. Available: http://dx.doi.org/10.1109/TMI.2009.2021471

- [9] C. Fritsch, J. Camacho, A. Ibanez, J. Brizuela, R. Giacchetta, R. Gonzalez, "A Full Featured Ultrasound NDE System in a Standard FPGA", in *Conf. Proc. (ECNDT 2006)*, pp.1–10.

- [10] J. Johansson, J. Delsing, "Microelectronics mounted on a piezoelectric transducer: Method, simulations, and measurements", *Ultrasonics*, vol. 44, pp. 1–11, 2006. [Online]. Available: http://dx.doi.org/10.1016/j.ultras.2005.06.004

- [11] M. Pollakowski, H. Ermert, "Chirp signal matching and signal power optimization in pulse-echo mode ultrasonic nondestructive testing", *IEEE Trans. Ultrason., Ferroelectr., Freq. Control*, vol. 41, pp. 655– 659, 1994. [Online]. Available: http://dx.doi.org/10.1109/58.308500

- [12] D. Campbell, et al., "A Compact High Voltage Nanosecond Pulse Generator", in Proc. ESA AME, pp.1–12, 2008.

- [13] J. Salazar, et al., "High-Power High-Resolution Pulser for Air-Coupled Ultrasonic NDE Applications", IEEE Trans. Instrum. and Meas., vol. 52, pp. 1792–1798, 2003. [Online]. Available: http://dx.doi.org/10.1109/TIM.2003.820445

- [14] L. Svilainis, A. Chaziachmetovas, V. Dumbrava, "Efficient high voltage pulser for piezoelectric air coupled transducer", *Ultrasonics*, vol. 53, pp. 225–231, 2013. [Online]. Available: http://dx.doi.org/10.1016/j.ultras.2012.06.004

- [15] D. Cowell, S. Freear, "Quinary excitation method for pulse compression ultrasound measurements", *Ultrasonics*, vol. 48, pp. 98– 108, 2008. [Online]. Available: http://dx.doi.org/ 10.1016/j.ultras.2007.10.001

- [16] G. K. Lewis, W. L. Olbricht, "Design and characterization of a high-power ultrasound driver with ultralow-output impedance", *Review of scientific instruments*, vol. 80, pp. 114704-1-8, 2009. [Online]. Available: http://dx.doi.org/10.1063/1.3258207

- [17] J. H. Kim, et al., "A high-voltage bi-polar pulse generator a using push-pull inverter", in Conf. 2003 IEEE (IECON 2003), pp. 102– 106.

- [18] X. Xu, J. T. Yen, K. K. Shung, "A Low-Cost Bipolar Pulse Generator for High-Frequency Ultrasound Applications", *IEEE Trans. Ultrason.*, *Ferroelectr.*, *Freq. Control*, vol. 52, pp. 443–447, 2007. [Online]. Available: http://dx.doi.org/10.1109/TUFFC.2007.259

- [19] V. Dumbrava, L. Svilainis, "The automated complex impedance measurement system", *Elektronika ir elektrotechnika*, no. 4, pp. 59– 62, 2007.

- [20] Non-destructive testing: Characterization and verification of ultrasonic examination equipment Part 1: Instruments. Standard EN 12668-1:2010.

- [21] G. Vanagas, D. Virzonis, V. Paukstaitis, D. Baranauskas, S. Cerviakov, "Integrated Front End Electronics Design for Micromachined Ultrasound Transducers", Elektronika ir elektrotechnika, no. 7, pp. 117–120, 2010.

- [22] I. Morkvenaite-Vilkonciene, D. Virzonis, G. Vanagas, V. Krikscikas, "Operating point of Capacitive Micromachined Ultrasonic Transducers with Sub-structural Elements", *Elektronika ir elektrotechnika*, vol. 18, no. 9, pp. 43–46, 2012.

- [23] L. Svilainis, V. Dumbrava, A. Chaziachmetovas, "Procedure for the recovery time estimation of the ultrasonic preamplifier", in *Proc.* (*BINDT 2013*), 2013, pp. 1–12.

- [24] L. Svilainis, V. Dumbrava, D. Kybartas, "Evaluation of the ultrasonic preamplifier noise voltage density", *Journal of Circuits, Systems and Computers*, vol. 23, no. 1, pp. 1450007-1-13, 2014.

- [25] L. Svilainis, K. Lukoseviciute, V. Dumbrava, A. Chaziachmetovas, "Subsample interpolation bias error in time of flight estimation by direct correlation in digital domain", *Measurement*, vol. 46, no. 10, pp. 3950–3958, 2013. [Online]. Available: http://dx.doi.org/10.1016/j.measurement.2013.07.038